# **ModelSim/Questa Tutorial**

Software Version 10.4

# **Table of Contents**

| Chapter 1 Introduction                                | 7  |

|-------------------------------------------------------|----|

| Introduction.  Download a Free PDF Reader With Search | 8  |

|                                                       |    |

| Chapter 2                                             |    |

| Conceptual Overview                                   | 9  |

| Design Optimizations                                  |    |

| Basic Simulation Flow                                 | 9  |

| Project Flow                                          |    |

| Multiple Library Flow                                 | 11 |

| Debugging Tools                                       | 12 |

| Chapter 3                                             |    |

| Basic Simulation                                      | 14 |

| Create the Working Design Library                     | 14 |

| Compile the Design Units                              | 16 |

| Optimize the Design                                   | 17 |

| Load the Design                                       | 17 |

| Run the Simulation                                    | 18 |

| Set Breakpoints and Step through the Source           | 20 |

| Chapter 4                                             |    |

| Projects.                                             | 25 |

| Create a New Project                                  | 25 |

| Add Objects to the Project                            | 26 |

| Changing Compile Order (VHDL)                         |    |

| Compile the Design                                    |    |

| Optimize for Design Visibility                        | 30 |

| Load the Design                                       | 30 |

| Organizing Projects with Folders                      | 31 |

| Adding Folders                                        |    |

| Moving Files to Folders                               |    |

| Using Simulation Configurations                       | 34 |

| Chapter 5                                             |    |

|                                                       | 37 |

| Creating the Resource Library                         | 37 |

| Creating the Project                                  | 39 |

|                                                       | 40 |

| Loading Without Linking Libraries                     | 40 |

| Verilog                                               | 40 |

|                                                       | 40 |

| Linking to the Resource Library                       | 41 |

| Chamton (                                             |           |

|-------------------------------------------------------|-----------|

| Chapter 6                                             | 42        |

| Simulating SystemC Designs                            | <b>43</b> |

| Setting up the Environment                            |           |

| Preparing an OSCI SystemC Design                      | 44        |

| Compiling a SystemC-only Design                       | 46        |

| Mixed SystemC and HDL Example                         | 47        |

| Viewing SystemC Objects in the GUI                    | 50        |

| Setting Breakpoints and Stepping in the Source Window | 51        |

| Examining SystemC Objects and Variables               | 53        |

| Removing a Breakpoint                                 | 54        |

| Chapter 7                                             |           |

| Analyzing Waveforms                                   | <b>56</b> |

| Loading a Design                                      |           |

| Add Objects to the Wave Window                        | 57        |

| Zooming the Waveform Display                          | 58        |

| Using Cursors in the Wave Window                      | 59        |

| Working with a Single Cursor                          | 59        |

| Working with Multiple Cursors                         | 60        |

| Saving and Reusing the Window Format                  | 61        |

|                                                       |           |

| Chapter 8                                             |           |

| Creating Stimulus With Waveform Editor                | <b>63</b> |

| Compile and Load the Design                           | 63        |

| Create Graphical Stimulus with a Wizard               | 64        |

| Edit Waveforms in the Wave Window                     | 66        |

| Save and Reuse the Wave Commands                      | 68        |

| Exporting the Created Waveforms                       | 69        |

| Run the Simulation                                    | 70        |

| Simulating with the Test Bench File                   | 71        |

| Importing an EVCD File                                | 72        |

| Chapter 9                                             |           |

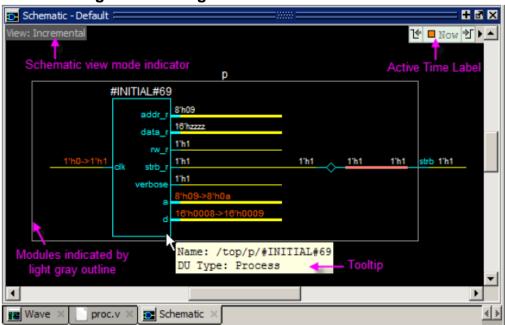

| Debugging With The Schematic Window                   | 74        |

| Compile and Load the Design                           | 74        |

| 1 0                                                   | 75        |

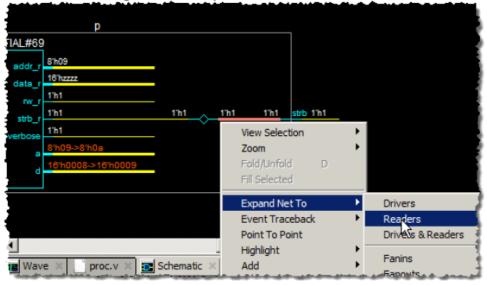

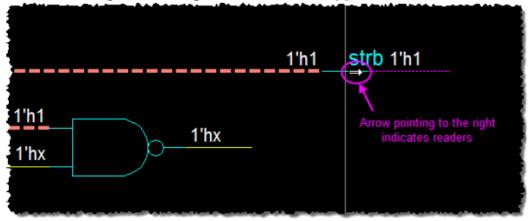

| Exploring Connectivity                                | 13        |

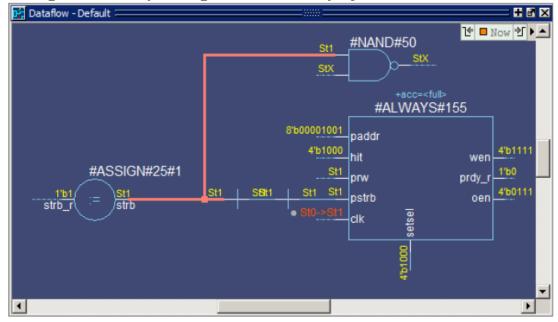

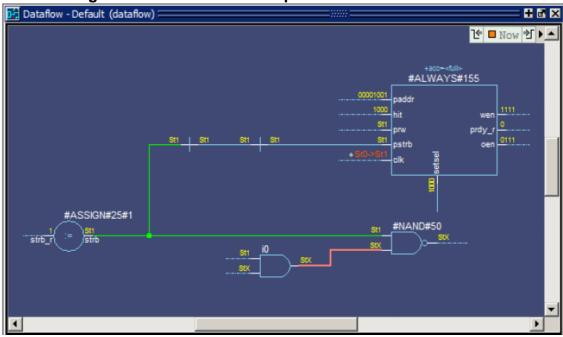

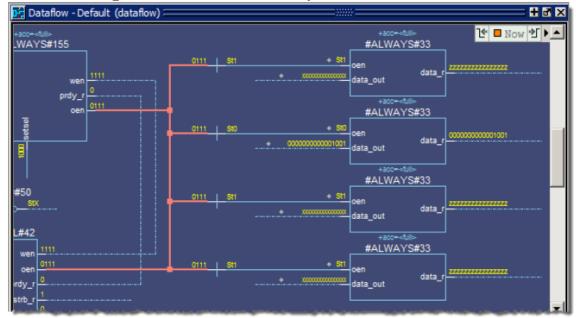

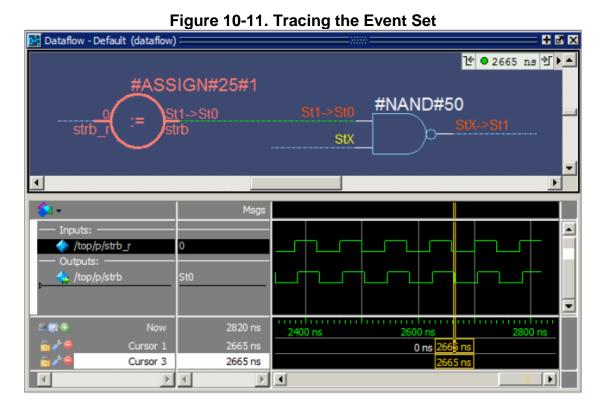

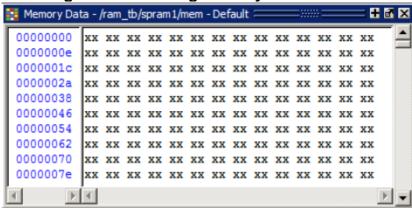

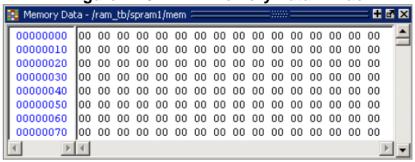

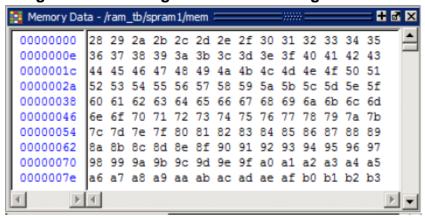

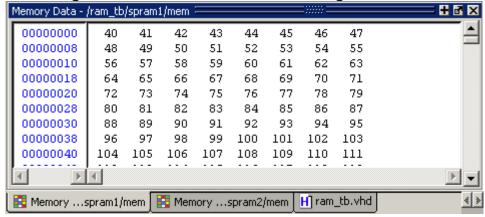

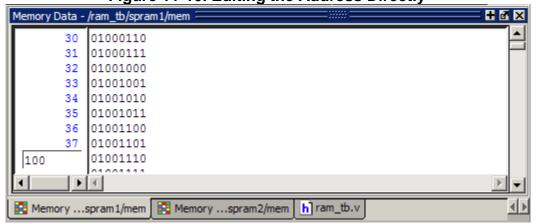

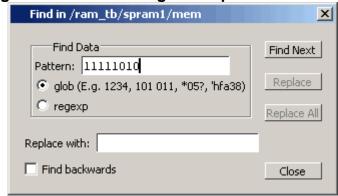

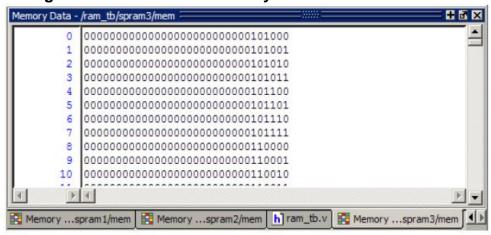

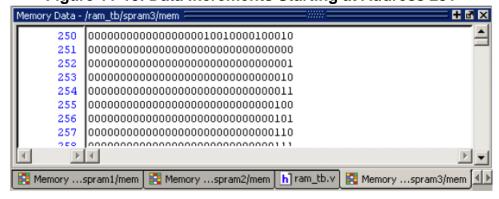

| Debugging With The Dataflow Window.90Compile and Load the Design90Exploring Connectivity91Tracing Events94Tracing an X (Unknown)98Displaying Hierarchy in the Dataflow Window100Chapter 11Viewing And Initializing Memories102Compile and Load the Design102View a Memory and its Contents103Navigate Within the Memory107Export Memory Data to a File108 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Compile and Load the Design90Exploring Connectivity91Tracing Events94Tracing an X (Unknown)98Displaying Hierarchy in the Dataflow Window100Chapter 11Viewing And Initializing Memories102Compile and Load the Design102View a Memory and its Contents103Navigate Within the Memory107                                                                     |

| Tracing Events94Tracing an X (Unknown)98Displaying Hierarchy in the Dataflow Window100Chapter 11Viewing And Initializing Memories102Compile and Load the Design102View a Memory and its Contents103Navigate Within the Memory107                                                                                                                          |

| Tracing an X (Unknown). 98 Displaying Hierarchy in the Dataflow Window 100  Chapter 11 Viewing And Initializing Memories 102 Compile and Load the Design 102 View a Memory and its Contents 103 Navigate Within the Memory 107                                                                                                                            |

| Displaying Hierarchy in the Dataflow Window                                                                                                                                                                                                                                                                                                               |

| Chapter 11Viewing And Initializing Memories102Compile and Load the Design102View a Memory and its Contents103Navigate Within the Memory107                                                                                                                                                                                                                |

| Viewing And Initializing Memories102Compile and Load the Design102View a Memory and its Contents103Navigate Within the Memory107                                                                                                                                                                                                                          |

| Viewing And Initializing Memories102Compile and Load the Design102View a Memory and its Contents103Navigate Within the Memory107                                                                                                                                                                                                                          |

| Compile and Load the Design102View a Memory and its Contents103Navigate Within the Memory107                                                                                                                                                                                                                                                              |

| Compile and Load the Design102View a Memory and its Contents103Navigate Within the Memory107                                                                                                                                                                                                                                                              |

| Navigate Within the Memory                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                           |

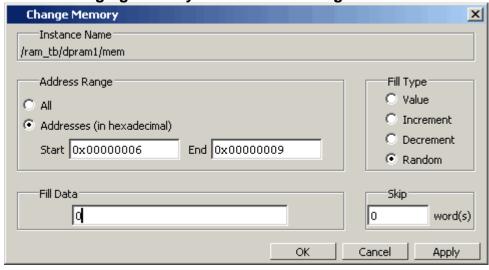

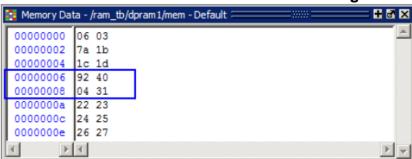

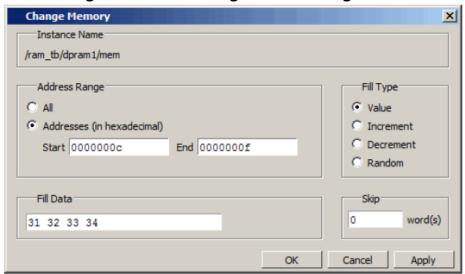

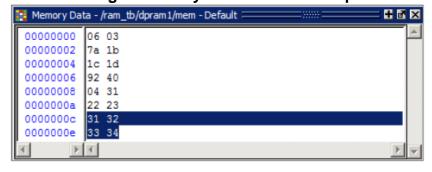

| Initialize a Memory                                                                                                                                                                                                                                                                                                                                       |

| Interactive Debugging Commands                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                           |

| Chapter 12                                                                                                                                                                                                                                                                                                                                                |

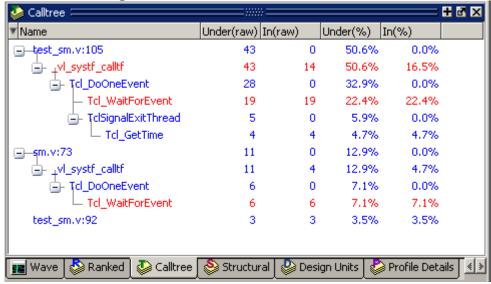

| Analyzing Performance With The Profiler                                                                                                                                                                                                                                                                                                                   |

| Compile and Load the Design                                                                                                                                                                                                                                                                                                                               |

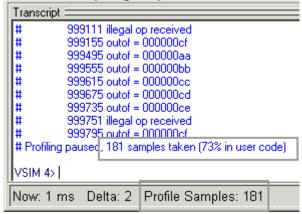

| Run the Simulation                                                                                                                                                                                                                                                                                                                                        |

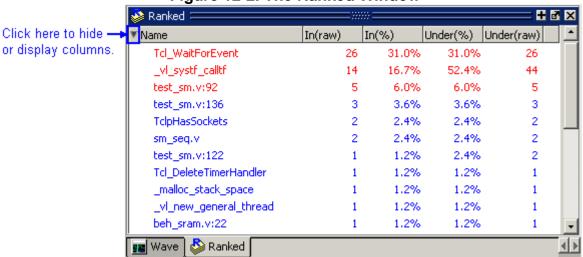

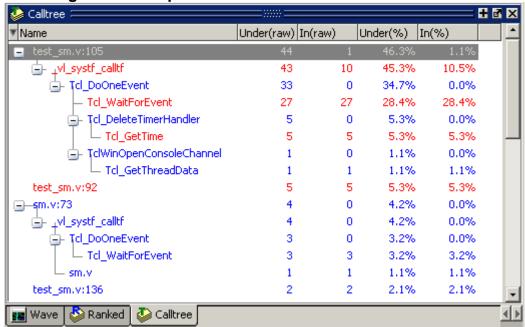

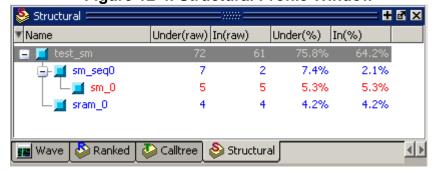

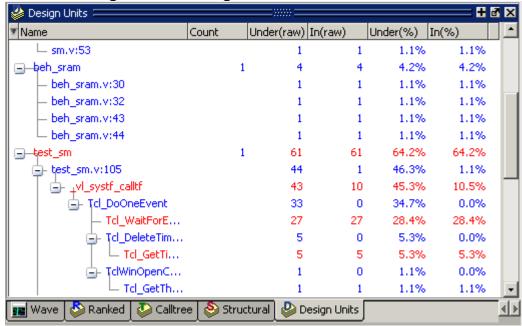

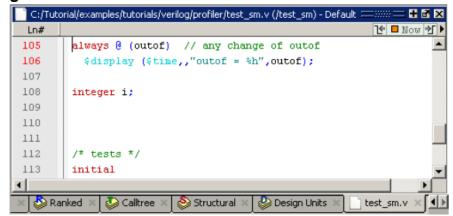

| View Performance Data in Profile Windows                                                                                                                                                                                                                                                                                                                  |

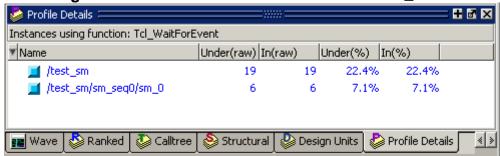

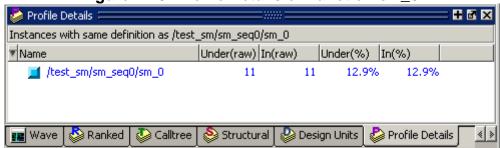

| View Profile Details                                                                                                                                                                                                                                                                                                                                      |

| Filtering the Data                                                                                                                                                                                                                                                                                                                                        |

| Creating a Performance Profile Report                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                           |

| Chapter 13                                                                                                                                                                                                                                                                                                                                                |

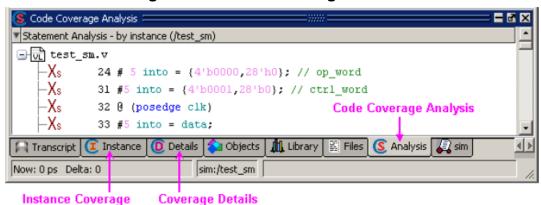

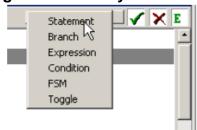

| Simulating With Code Coverage                                                                                                                                                                                                                                                                                                                             |

| Compile the Design                                                                                                                                                                                                                                                                                                                                        |

| Load and Run the Design                                                                                                                                                                                                                                                                                                                                   |

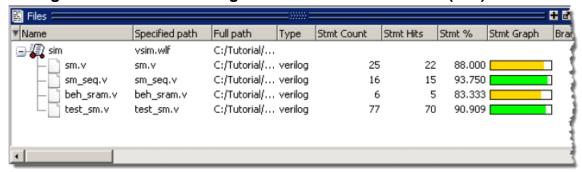

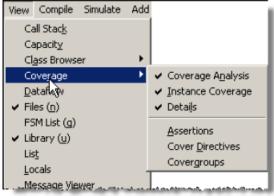

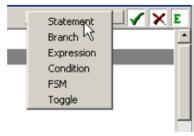

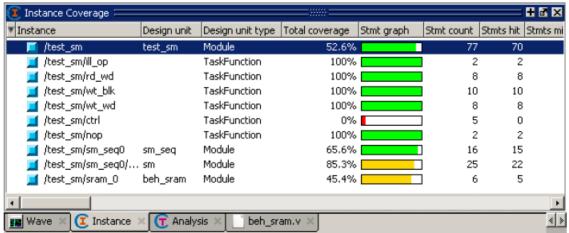

| Viewing Coverage Data                                                                                                                                                                                                                                                                                                                                     |

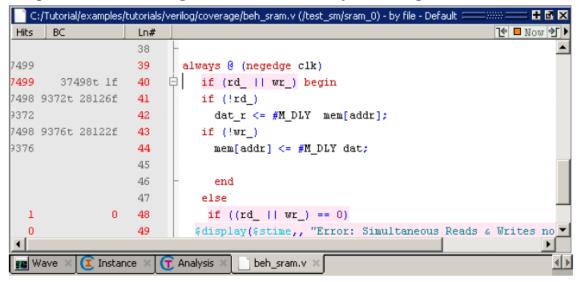

| Coverage Statistics in the Source Window                                                                                                                                                                                                                                                                                                                  |

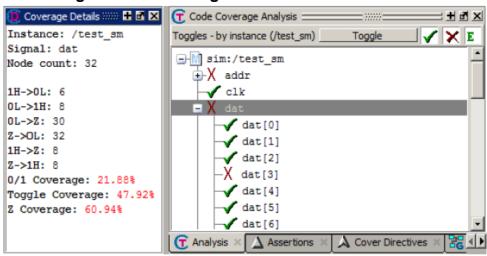

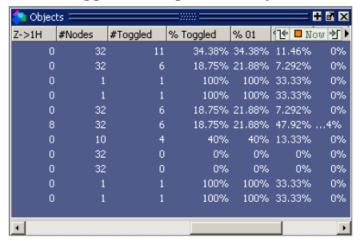

| Toggle Statistics in the Objects Window                                                                                                                                                                                                                                                                                                                   |

| Excluding Lines and Files from Coverage Statistics                                                                                                                                                                                                                                                                                                        |

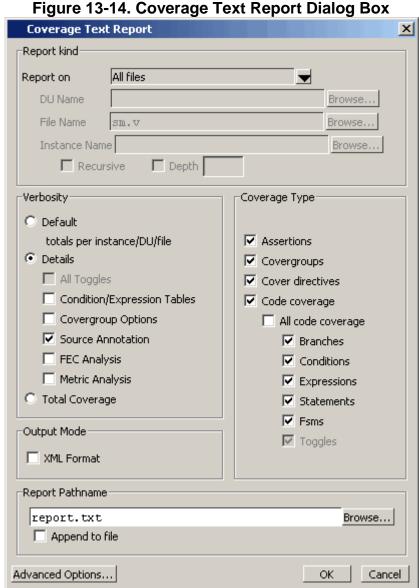

| Creating Code Coverage Reports                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                           |

| Chapter 14                                                                                                                                                                                                                                                                                                                                                |

| Debugging With PSL Assertions                                                                                                                                                                                                                                                                                                                             |

| Run the Design without PSL Assertions                                                                                                                                                                                                                                                                                                                     |

| Using Assertions to Speed Debugging                                                                                                                                                                                                                                                                                                                       |

| Debugging the Assertion Failure                                                                                                                                                                                                                                                                                                                           |

| Cha | pter 1 | <b>5</b> |

|-----|--------|----------|

|     |        |          |

| SystemVerilog Assertions and               |             |

|--------------------------------------------|-------------|

| Functional Coverage.                       | 149         |

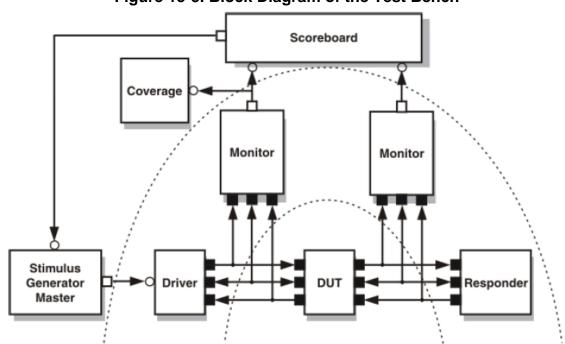

| Understanding the Interleaver Design       | 149         |

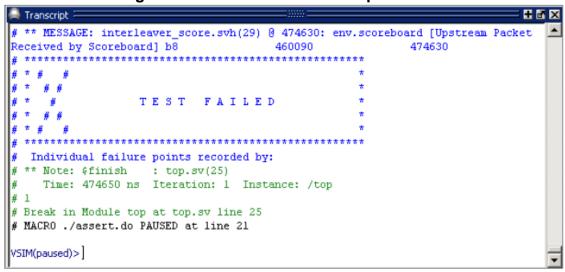

| Run the Simulation without Assertions      | 151         |

| Run the Simulation with Assertions         | 152         |

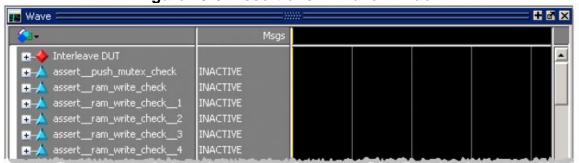

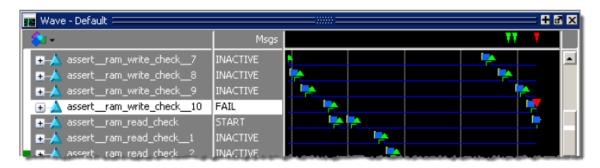

| Debugging with Assertions                  | 154         |

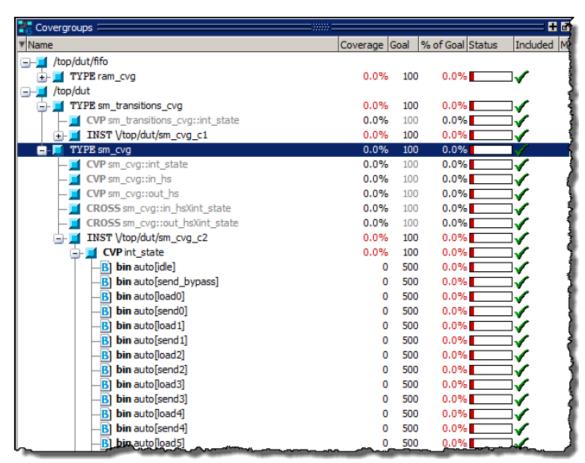

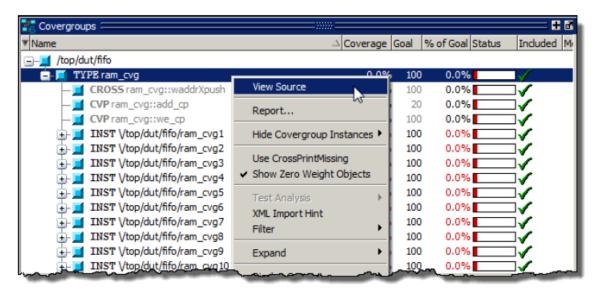

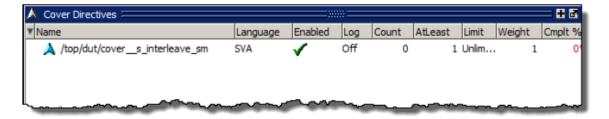

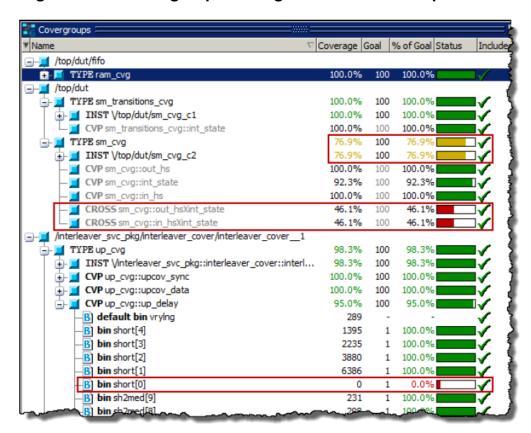

| Exploring Functional Coverage              | 160         |

| Creating Functional Coverage Reports       | 170         |

| Chapter 16                                 |             |

| Using the SystemVerilog DPI                | <b>17</b> 3 |

| Examine the Source Files                   | 173         |

| Exploring the Makefile                     | 177         |

| Exploring the <i>windows.bat</i> File      | 179         |

| Compile and Load the Simulation            | 180         |

| Run the Simulation                         | 180         |

|                                            | 100         |

| Chapter 17                                 |             |

| Using SystemVerilog DPI for Data Passing   | 183         |

| Mapping Verilog and C                      |             |

| Design Files for This Lesson               | 184         |

| Examine the Source Files                   | 186         |

| Explore the Makefile                       | 186         |

| Explore the <i>windows.bat</i> File        | 187         |

| Compile and Load the Simulation            | 188         |

| Run the Simulation                         | 188         |

| Chapter 18                                 |             |

| Comparing Waveforms                        | 193         |

| Creating the Reference Dataset             | 193         |

| Creating the Test Dataset                  | 194         |

| Comparing the Simulation Runs              | 195         |

| Viewing Comparison Data.                   | 197         |

| Comparison Data in the Wave Window         | 197         |

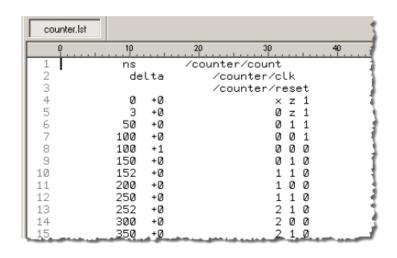

| Viewing Comparison Data in the List Window | 198         |

| Saving and Reloading Comparison Data       | 199         |

| Saving and Reloading Comparison Data       | 177         |

| Chapter 19                                 |             |

| Automating Simulation                      | <b>20</b> 2 |

| Creating a Simple DO File                  | 202         |

| Running in Command-Line Mode               | 203         |

| Using Tcl with the Simulator               | 206         |

#### **Chapter 20**

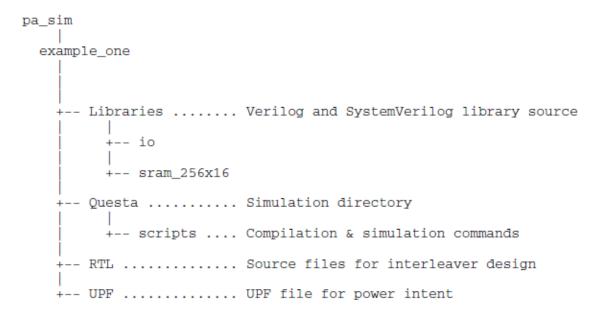

| Getting Started With Power Aware       | <u>. 209</u> |

|----------------------------------------|--------------|

| Create a Working Location              | . 210        |

| Compile the Source Files of the Design | . 210        |

| Annotate Power Intent                  | . 211        |

| Specifying Power Aware Options         | . 212        |

| Simulate the Power Aware Design        | . 212        |

| Analyze Results                        | . 213        |

# Chapter 1 Introduction

아시다시피 ModelSim 과 Questa 는 FPGA/ASIC을 개발하는데 있어서 꼭 있어야 하는 필수 HDL Simulator 입니다. 사용법도 상당히 쉽게 되어 있어서 Tool 에 대한 사전 지식이 없어도 편리하고, 익숙하게 사용할 수 있도록 많은 문서들을 같이 제공하고 있습니다.

해당 문서들은 Tool 이 설치되면 자동으로 같이 설치가 되어 영문 PDF, HTML 형태로 제공이되고 있고, Windows 환경에서 혹은 Linux, Solaris 의 CDE, KDE, GNOME 환경에서 보실 수 있습니다.

각 문서들은 아래의 표를 통해서 보실 수 있습니다.

| 문서 종류                                             | 파일 포맷        | 보는 방법 (Tool 동작시 )                         |

|---------------------------------------------------|--------------|-------------------------------------------|

| Installation & Licensing<br>Guide                 | PDF          | Help > PDF Bookcase                       |

|                                                   | HTML and PDF | Help > InfoHub                            |

| Quick Guide (command and feature quick-reference) | PDF          | Help > PDF Bookcase and<br>Help > InfoHub |

| Tutorial                                          | PDF          | Help > PDF Bookcase                       |

|                                                   | HTML and PDF | Help > InfoHub                            |

| User's Manual                                     | PDF          | Help > PDF Bookcase                       |

|                                                   | HTML and PDF | Help > InfoHub                            |

| Command Reference Manual                          | PDF          | Help > PDF Bookcase                       |

|                                                   | PDF          | Help > InfoHub                            |

| Graphical User Interface                          | PDF          | Help > PDF Bookcase                       |

| (GUI) Reference Manual                            | PDF          | Help > InfoHub                            |

| Foreign Language<br>Interface Manual              | PDF          | Help > PDF Bookcase                       |

|                                                   | HTML         | Help > InfoHub                            |

| OVL Checkers Manager<br>User's Guide              | PDF          | Help > PDF Bookcase                       |

|                                                   | HTML         | Help > InfoHub                            |

| Power Aware Simulation                            | PDF          | Help > PDF Bookcase                       |

| User's Manual                                     | HTML         | Help > InfoHub                            |

| Command Help               | ASCII | type <b>help [command name]</b> at the prompt in the Transcript pane                          |

|----------------------------|-------|-----------------------------------------------------------------------------------------------|

| Error message help         | ASCII | type <b>verror</b> < <b>msgNum&gt;</b> at the Transcript or shell prompt                      |

| Tcl Man Pages (Tcl manual) | HTML  | select <b>Help &gt; Tcl Man Pages</b> , or find contents.htm in \modeltech\docs\tcl_help_html |

| Technotes                  | HTML  | available from the support site                                                               |

## **Download a Free PDF Reader With Search**

ModelSim/Questa PDF 문서를 보기 위해서는 Adobe Acrobat Reader 가 필요합니다. Reader 는 무료로 사용이 가능하며, 아래의 주소를 통해 다운로드 받으실 수 있습니다.

www.adobe.com

# Chapter 2 Conceptual Overview

ModelSim/Questa 는 VHDL, Verilog, SystemVerilog, SystemC 그리고 mixed-language 로 설계된 Design 을 Simulation 하는 제품입니다.

이번 챕터에서는 ModelSim/Questa 를 통해 Simulation 을 진행하는데 있어 다음 5가지 방법에 간략하게 알아보겠습니다.

- Design Optimizations 최근에 발표되는 ModelSim/Questa 의 Default Mode 입니다.

- Basic Simulation flow 챕터 3 에서 자세히 살펴보겠습니다.

- Project flow 챕터 4 에서 자세히 살펴보겠습니다.

- Multiple library flow 챕터 5 에서 자세히 살펴보겠습니다.

- Debugging tools 챕처 6 이후부터 기능을 하나씩 살펴보겠습니다.

# **Design Optimizations**

Basic simulation flow 에 대해 알아보기 전에, Design Optimization 기능에 대해 확실하게 개념을 잡는 것이 중요합니다. ModelSim/Questa 는 기본적으로 Optimization Mode 가 Default Mode 로 되어 있습니다. Optimization Mode 로 동작을 하면 Simulation Performance 는 약 10 배 정도의 이득을 볼 수 있습니다. 대신에 Simulation 결과를 Wave window 를 통해 보는데 있어서는 제약이 따르게 됩니다. 물론 유저 분이 중요하다고 생각되는 특정한 모듈이나 signals에 대해서는 옵션을 통해 제약을 해제할 수도 있습니다.

따라서, 최선의 방법은 유저 분이 Design 상의 정보 중 어떤 것을 Optimization 을 하고 어떤 것을 Optimization 을 하지 않을 것인지 결정을 하여 Design 을 최적화 하는 것입니다. ModelSim/Questa 에서는 위에서 언급한 내용처럼 디폴트 모드가 Optimization 모드로 되어 있고, vopt command 를 사용할 수도 있습니다. vopt command 사용법은 Modelsim/Questa 의 User Manual 중에 Optimization Design with vopt 챕터를 보시면 자세히 나와 있습니다.

### **Basic Simulation Flow**

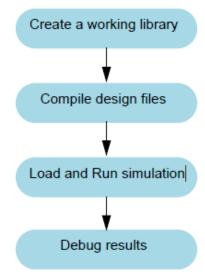

유저 분이 Design 을 ModelSim/Questa 틀 통해 Simulation 을 하기 위한 가장 기본적인 것들을 이번엔 살펴볼 것입니다. ModelSim/Questa 의 Basic Simulation Flow 는 아래의 그림을 보시면 됩니다.

Figure 2-1. Basic Simulation Flow - Overview Lab

#### Creating a working library

ModelSim/Questa 에서 Simulation을 진행하기 위해서는 모든 Design 이 Compile 된 Library 가 있어야 합니다. 일반적으로 새로운 Simulation 을 하기 위해 Tool 을 구동했으면 제일 먼저 work 라는 이름으로 불리는 Working library 를 만드는 단계입니다.

#### Compiling design files

Working library 를 만들었으면 이제는 Library 에 Design file 을 Compile 해야 합니다. Compile 된 라이브러리는 다른 Platform 에서 진행 할 경우 다시 Re-Compile 할 필요 없이 바로 사용이 가능합니다.

#### Load and run simulation

모든 Design 이 Compile 이 되었으면, Simulator 에 top-level module 을 invoke 합니다. Design 이 성공적으로 load 가 되면, Run command 를 이용하여 simulation 을 진행합니다.

#### Debug

Simulation 진행으로 얻어진 결과가 완벽하지 않다면, ModelSim/Questa 의 debug 기능을 이용하여 debugging 을 합니다.

# **Project Flow**

Project Flow 는 HDL design 을 Simulation 하는 방법 중에 한가지 입니다. Project Flow 를 이용하면 매우 편리하게 Design file 을 관리하고 Simulation 결과를 지정할 수 있습니다. 하지만,

ModelSim/Questa 를 사용하시면서 꼭 Project Flow 를 사용할 필요는 없습니다. Basic Flow 와 Project Flow 중에 유저 분이 편한 대로 진행하시면 됩니다.

아래의 그림은 Project Flow 방식의 진행 순서를 보여주고 있습니다.

Create a project

Add files to the project

Compile design files

Run simulation

Debug results

위의 Flow 처럼 Project Flow 를 통한 Simulation 진행 순서는 Basic Simulation 과 상당히 유사합니다. 하지만 다른 점도 있습니다.

- 유저 분이 직접 Working library 는 만들 필요가 없습니다. Project 를 만들 때 자동으로 Library 가 만들어 집니다.

- 작업하고 있는 Project 는 지속됩니다. ModeSim/Questa 를 종료 후 다시 실행할 때 최근에 작업했던 Project 가 자동으로 열립니다.

# **Multiple Library Flow**

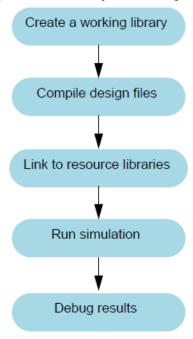

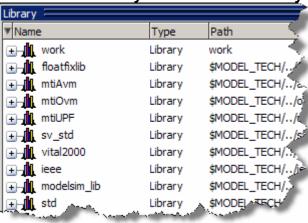

ModelSim/Questa 에서 Library 를 사용하는 방법에는 2가지 방법이 있습니다. 첫 번째는 Design 이 컴파일 된 로컬 library 를 사용하는 방법과 두 번째로 Resource library 를 사용하는 방법이 있습니다. Working library 를 이용할 때 만약 Design 의 변경이 있다면 Recompile 을 해주어야 합니다. Resource library 는 유저가 생성 할 수 있으며, 디자인을 위해 부품 역할을 할수 있도록 실리콘 공급 업체에 의해서 제공받을 수도 있습니다

아래의 그림은 Multiple Library Flow 를 보여주고 있습니다.

Figure 2-3. Multiple Library Flow

Project Flow 를 통해 진행을 할 때도 Link to resource libraries 를 할 수 있습니다. Project Flow 를 통해 진행하고 있다면 맨 위의 Create a working library 단계를 create the project 와 add the testbench to the project 의 2 스텝 단계로 변경하여 진행하시면 됩니다.

# **Debugging Tools**

ModelSim/Questa 에는 Design 을 분석하고 디버깅할 수 있는 많은 기능들을 가지고 있습니다.

- Using projects

- Working with multiple libraries

- Simulating with SystemC

- Setting breakpoints and stepping through the source code

- Viewing waveforms and measuring time

- Exploring the "physical" connectivity of your design

- Viewing and initializing memories

- Creating stimulus with Waveform Editor

- Analyzing simulation performance

- Testing code coverage

- Comparing waveform

- Debugging with PSL assertions

- Using SystemVerilog assertion and cover directives

- Using the SystemVerilog DPI

- Automating simulation

# **Chapter 3 Basic Simulation**

이번 챕터에서는 ModelSim./Questa 를 통해 Basic Simulation 하기 위해 아래의 단계별로 순차적으로 진행을 할 것입니다.

- 1. Create the working library

- 2. Compile the Design Units

- 3. Optimize the Design

- 4. Load the Design

- 5. Run the Simulation

이번 챕터부터는 예제 파일을 가지고 작업을 진행할 것입니다. 이번 챕터의 예제 파일은 8bit binary up counter 이며 해당 파일은 ModelSim/Questa 를 설치된 경로 안에 있습니다.

**Verilog** — <install\_dir>/examples/tutorials/verilog/basicSimulation/counter.v and tcounter.v **VHDL** — <install\_dir>/examples/tutorials/vhdl/basicSimulation/counter.vhd and tcounter.vhd

예제 파일들은 Verilog 와 VHDL 둘 다 지원을 하고 있습니다. 가지고 계신 ModelSim/Questa 의 License 에 따라 해당하는 언어 예제를 선택하시면 됩니다.

## **Create the Working Design Library**

Design 을 Simulation 을 하기 전에 먼저 Library 를 만들어 Compile 을 해야 합니다.

- 1. 새로운 디렉토리를 만들어 예제 파일을 그 디렉토리에 Copy 합니다.

- A. ModeSim/Questa 를 실행합니다.

단축 아이콘을 클릭하거나 명령프롬프트에 vsim command 를 입력하면 ModelSim/Questa 의 GUI 가 올라옵니다.

GUI 가 올라오면 File>Change Directory 를 통해 1번에서 만든 디렉토리로 이동합니다.

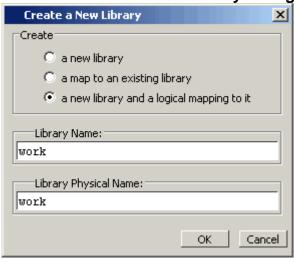

2. Working library 를 만듭니다.

Figure 3-1. The Create a New Library Dialog Box

B. 보여지는 Dialog 창에서 Library name 과 Physical name(실제로 만들어지는 디렉토리)에 work 라고 입력합니다 입력이 끝났으면 OK 버튼을 클릭합니다.

Figure 3-2. work Library Added to the Library Window

OK 버튼을 클릭하면 Library 윈도우에 library 가 만들어 진 것을 확인 할 수 있습니다.

위에서의 작업을 command 로 작업을 하기 위해선 아래의 command 를 입력해 주면 됩니다.

vib work vmap work work

# **Compile the Design Units**

Work library 가 만들어 졌으면, 이제 Compile 을 할 차례입니다.

- 1. Copy 를 한 예제 파일들을 Compile 을 할 것 입니다.

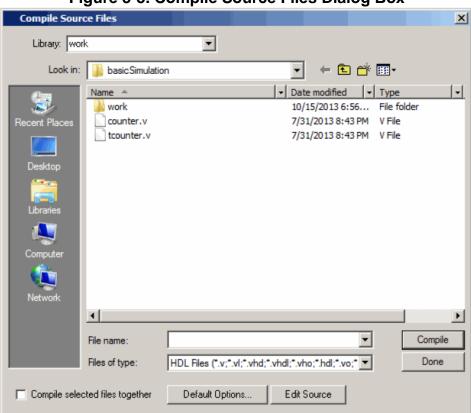

- A. ModelSim/Questa 의 메뉴 중에 Compile>Compile 을 선택합니다.

만약에 해당하는 메뉴가 보여지지 않으면 Project Flow 상태일 수도 있습니다. Project Flow 상태이면 File>Close 를 선택해 주시면 Project 가 종료되며 원하시는 메뉴를 선택할 수 있습니다.

- B. Compile 창이 열리면 Copy 한 2개의 파일 counter.v tcounter.v 파일을 선택하고 Compile 버튼을 클릭합니다. 그러면 Work library 안에 해당 파일이 compile 이 됩니다.

- C. 두 개의 파일을 Compile 을 했으면 Done 버튼을 클릭합니다.

Figure 3-3. Compile Source Files Dialog Box

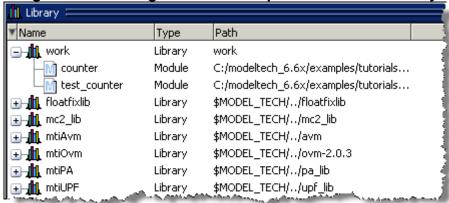

- 2. Compile 한 결과를 확인할 것입니다.

- A. Library 윈도우를 보면 Work library 옆에 "+" 아이콘이 보이실 겁니다. "+" 를 클릭하면 2개의 Design unit 이 보일 것입니다.

Figure 3-4. Verilog Modules Compiled into work Library

# **Optimize the Design**

- 1. vopt command 를 이용하여 Full visibility 가 가능한 Optimize design 을 만들 것입니다.

- A. ModelSim/Questa 의 GUI 에서 하단부에 있는 Transcript 윈도우에 아래의 command 를 입력합니다.

vopt +acc test\_counter -o testcounter\_opt

+acc 는 visibility 관련 옵션이며, -o 는 결과 파일 이름을 지정하는 옵션입니다.

주의 : vopt command 를 사용할 때 같은 이름으로는 결과 파일이 만들어 지지 않습니다.

# **Load the Design**

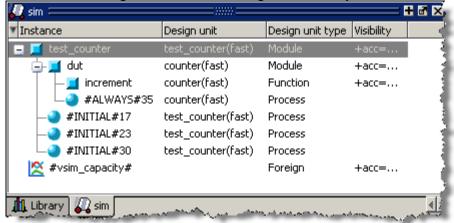

- 1. 이제는 test\_counter module 을 Simulator 에 Loading 할 것입니다.

- A. Design loading 은 vsim command 를 통해 이루어 집니다. 전 단계에서 만들어 놓은 Optimize design 을 사용하기 위해 아래의 command 를 입력합니다.

#### vsim testcounter\_opt

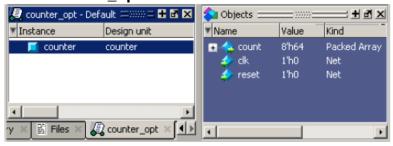

Design 이 Load 가 되면 Structure 윈도우에 해당하는 Design 정보를 볼 수 있습니다.

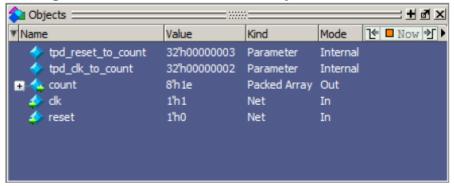

Figure 3-5. The Design Hierarchy

추가적으로 Objects 와 Process 윈도우가 열리게 됩니다. Object 윈도우에서는 Structure 윈도우에서 선택한 Module 이 가지고 있는 Data 에 대한 정보를 볼 수 있습니다. 확인 할 수 있는 Data 는 signals, net, register, constants, variable 과 디자인상에서 선언된 process, generics, parameters 와 SystemC module 의 Data variable 입니다.

Process 윈도우에서는 HDL, SystemC process 정보를 4가지 모드 -Active, In region, Design, Hierarchical-로 보여줍니다.

陷 Objects : ⅎⅎⅆϫ = ;;;;;;; Value Kind ▼ Name 上 Now → ト Mode dk 1'hx Register Internal 1hx Internal reset Register 8'hxx Internal 🕳 🔷 count Net 🎇 Processes (Active) 🗆 ₹ Name Type (filtered) State Order

Figure 3-6. The Object Window and Processes Window

### **Run the Simulation**

이제 Simulation 을 진행하기 위한 준비단계가 끝났습니다. 이제 Wave 윈도우에 signal 을 추가하고 Simulation 을 진행할 것입니다.

#### 1. Wave 윈도우 열기

A. **view wave** 라는 command 를 입력합니다.

command 를 입력하면 화면 오른쪽에 Wave 윈도우가 나타납니다. 물론 GUI 를 통해서도 Wave 윈도우를 열 수 있습니다. View>Wave 를 선택하시면 마찬가지고 화면 오른쪽에 윈도우가 나타납니다.

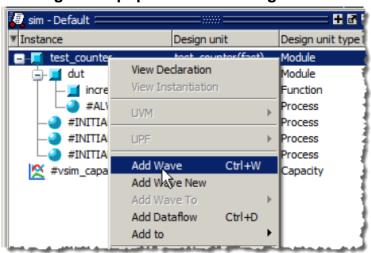

- 2. Wave 윈도우에 Signal 추가하기

- A. Structure(sim) 윈도우에서 test\_counter 모듈을 선택하고 마우스 오른쪽 버튼을 클릭하면 팝업 메뉴가 열립니다.

- B. 팝업메뉴에서 Add>To Wave>All items in region 을 선택하면 Design 의 모든 signal 이 Wave 윈도우에 추가 됩니다.

Figure 3-7. Using the Popup Menu to Add Signals to Wave Window

#### 3. Simulation 시작하기

A. Run 아이콘을 클릭 합니다.

Run 아이콘을 클릭하면 100ns 만큼 Simulation 이 진행되며, 그 결과가 Wave 윈도우에 표시됩니다.

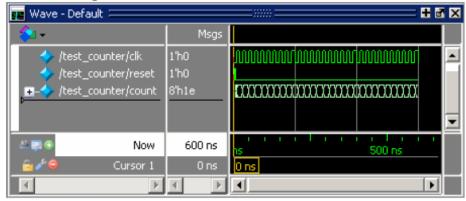

B. Transcript 윈도우에 500 이라고 입력하면, Simulation 은 기존의 100ns 에서 500ns 만큼 추가적으로 진행되어 총 600ns 까지의 Simulation 결과는 Wave 윈도우에서 확인할 수 있습니다.

Figure 3-8. Waves Drawn in Wave Window

C. 메인 윈도우나 Wave 윈도우에서 Run-All 아이콘을 클릭합니다.

그러면, Simulation 은 Design 상에 Break -Verilog 의 \$stop-부분까지 혹은 외부에서 강제로 Break 를 걸 때까지 Simulation 이 진행됩니다.

위의 아이콘이 Break 아이콘 입니다.

## Set Breakpoints and Step through the Source

이제는 Debugging 을 하기 위해 Breakpoint 를 Source code 안에 삽입을 할 것입니다. Break point 를 설정하고 Simulation 을 진행하면 Simulation 은 해당 break point 에서 멈춥니다. Break point 는 Source code 중에 실행이 되는 Line 에 설정 할 수 있고, 설정 가능한 Line 은 Source 윈도우상에 빨간색 Line number 로 표시됩니다.

- 1. Source 윈도우에서 counter.v 코드 열기

- A. 메인 메뉴에서 View>Files 를 선택해 Files 윈도우를 엽니다.

- B. Files 윈도우에서는 현재 진행중인 Simulation 에 대한 정보가 나오며 "+" 를 클릭하면 File 리스트를 볼 수 있습니다.

- C. File 리스트 중에서 counter.v 를 더블 클릭하면 Source 윈도우에 해당 파일이 열립니다.

#### 2. Break point 설정하기

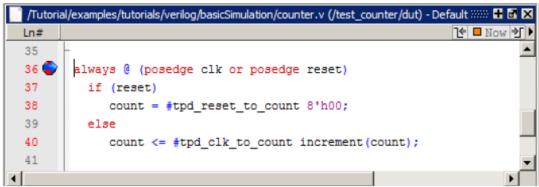

A. Source 윈도우에서 열린 counter.v 파일의 36번 Line 까지 마우스 스크롤을 이용하여 이동합니다. 윈도우의 36번 라인에 Line 숫자 부분을 클릭하면 Line 옆에 빨간색 공이 생기며 Break point 가 설정됩니다.

Figure 3-9. Setting Breakpoint in Source Window

```

🧂 /Tutorial/examples/tutorials/verilog/basicSimulation/counter.v (/test_counter/dut) - Default :::::: 🛨 🗗 🔀

Ln#

T ■ Now

35

36

always @ (posedge clk or posedge reset)

37

if (reset)

38

count = #tpd_reset_to_count 8'h00;

39

40

count <= #tpd_clk_to_count increment(count);</pre>

41

Wave

counter.v ×

```

- 3. Break point 삭제 및 활성화, 비활성화 시키기

- A. break point 가 만들어진 Line 에서 해당 Line 의 숫자 부분을 다시 클릭합니다. 빨간색 공이 검정색 공이 되며 비활성화 됩니다.

- B. 다시 해당 Line 을 클릭하면 빨간 색 공이 되며 활성화 됩니다.

- C. Break point 를 삭제하기 위해서는 해당 Break point 에서 마우스 오른쪽 버튼을 클릭하고 Remove Breakpoint 36 클릭 하시면 해당 Break point 가 삭제됩니다.

- D. 다시 36 번 라인에 Break point 를 만들고 활성화 시킵니다.

#### 4. Simulation 다시 시작하기

A. 현재 진행하고 있는 Simulation 을 Reload 하기 위해서는 Restart 아이콘을 클릭하면 됩니다.

Restart 아이콘을 클릭하면 아래와 같은 창이 나타납니다.

Ē

Figure 3-10. Setting Restart Functions

- B. 전체를 체크하고 Restart 버튼을 클릭합니다.

- C. Run-All 아이콘을 클릭 합니다.

이제 Simulation 은 위에서 설정한 36번 Line 에 도달할 때까지 Simulation 이 진행됩니다. Simulation 이 해당 Break point 에 도달하면 Simulation 은 멈추고 해당 파일이 Source 윈도우에 열리며, 파란색 화살표 마크가 해당 Line 에 표시됩니다.

Figure 3-11. Blue Arrow Indicates Where Simulation Stopped.

일반적으로 Break point 에 의해 Simulation 이 멈추면 유저들은 더 많은 현 상태에서의 더 많은 정보를 얻기를 원할 것 입니다. 이제 그 정보를 얻을 수 있는 여러 옵션에 대해 살펴보겠습니다.

우선 Object 윈도우를 통해 signal value 를 확인하겠습니다.

≣ŧ

Figure 3-12. Values Shown in Objects Window

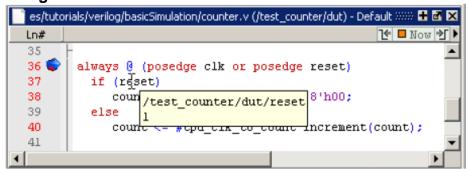

Source 윈도우에서 보여지는 Design 코드상의 highlight 처리된 signal 혹은 parameter, variable 위에 마우스 포인트를 놓으면 Wave Window 에서 cursor 가 선택된 부분의 변수 값이 노란 박스로 표시됩니다.

Figure 3-13. Hover Mouse Over Variable to Show Value

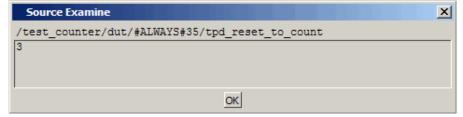

또한 Design 코드상의 highlight 처리된 signal 혹은 parameter, variable 위에 마우스 포인트를 놓고 마우스 오른쪽 버튼을 클릭하여 Examine 을 선택하면 현재의 Value 가 창에 표시가 됩니다.

Figure 3-14. Parameter Name and Value in Source Examine Window

examine 라는 command 를 입력을 해서 Value 를 확인할 수 있습니다.

EX) examine count

#### 5. Step command 를 활용하기

A. 메인 메뉴의 아이콘 중 step 아이콘을 클릭합니다.

Step 아이콘은 debugger 기능입니다.

Step 아이콘을 클릭하거나 step command 를 입력하면 현재 멈추어져 있는 Simulation 이 Code 한 줄 한 줄씩 실행이 되어 갑니다.

#### 6. Simulation 종료하기

A. Simulate>End Simulation 을 선택하면 현재 진행중인 Simulation 이 종료 됩니다.

# Chapter 4 Projects

이번 챕터에서는 3장에서 진행했던 Simulation 방법을 Project Flow 방식으로 진행 할 것입니다. Project Flow 를 통해 작업을 하면 .mpf 파일이 만들어지고 Project 는 아래와 같은 정보로 구성 됩니다.

- HDL Source 파일을 저장하거나 Reference 경로

- Source 파일 외에 다른 문서(READMEs, Documentation)

- Local library

- Reference global library

이번 챕터부터는 예제 파일을 가지고 작업을 진행할 것입니다. 이번 챕터의 예제 파일은 8bit binary up counter 이며 해당 파일은 ModelSim/Questa 를 설치된 경로 안에 있습니다.

**Verilog** – <install\_dir>/examples/tutorials/verilog/projects/counter.v and tcounter.v

**VHDL** – <install\_dir>/examples/tutorials/vhdl/ projects /counter.vhd and tcounter.vhd

예제 파일들은 Verilog 와 VHDL 둘 다 지원을 하고 있습니다. 가지고 계신 ModelSim/Questa 의 License 에 따라 해당하는 언어 예제를 선택하시면 됩니다.

## **Create a New Project**

- 1. 새로운 디렉토리를 만들고 예제 파일은 해당 디렉토리로 Copy 하기

- A. ModeSim/Questa 를 실행합니다

단축 아이콘을 클릭하거나 vsim command 를 입력하면 ModelSim/Questa 의 GUI 가 올라옵니다.

만약 지난 챕터를 이어서 바로 시작하시는 경우엔 ModelSim/Questa 가 구동 되어 있으니 다시 실행할 필요가 없습니다.

File>Change Directory 에서 위에서 만든 디렉토리로 지정합니다.

#### 2. Project 만들기

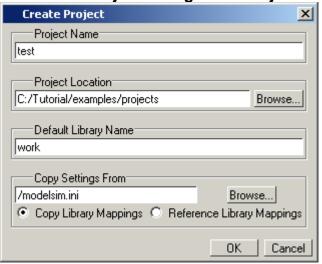

A. 메인 메뉴에서 File>New>Project 를 선택합니다.

메뉴를 선택하면 Create Project 창이 열립니다. 이 창에서 유저 분은 Project name, Project Location-directory, default library name, Modelsim/Questa 설정 파일인 .ini 파일 등을 지정할 수 있습니다.

- B. Project name 을 test 로 입력합니다.

- C. Browse 버튼을 클릭해서 Project 를 저장할 디렉토리를 지정합니다.

- D. Default library 이름을 work 로 입력합니다.

- E. OK 를 클릭합니다.

Figure 4-1. Create Project Dialog Box - Project Lab

### Add Objects to the Project

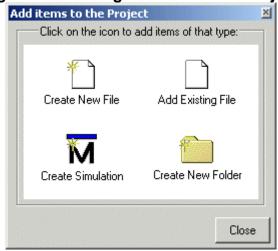

앞선 순서에서 OK 버튼을 클릭하면서 Project 를 위한 기본적인 설정은 끝났습니다. 그리고 이 제 ModelSim/Questa 의 GUI 상에 Add items to the Project 라는 창이 나타납니다.

Figure 4-2. Adding New Items to a Project

이 창을 통해 유저 분은 Project 에 해당하는 작업을 할 수 있습니다.

새로운 파일(Create New File) 을 만들거나, 기존의 파일(Add Existing File) 을 추가하거나, Simulation Configuration 파일(Create Simulation) 을 만들거나, Project 내에 디렉토리(Create New Folder) 를 만들 수 있습니다.

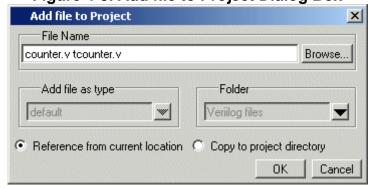

#### 1. 2개의 파일을 추가하기

A. Add Existing File 을 선택합니다.

파일을 추가할 때에는 Project 가 위치한 디렉토리에 Copy 를 할 수도 있고, Project 내에 위치 경로만 지정하는 Reference 방법 2가지가 있습니다.

Figure 4-3. Add file to Project Dialog Box

- B. Browse 버튼을 클릭하여 Copy 한 2개의 파일을 선택합니다.

- C. 파일을 선택하고 Reference form current location 을 선택하고 OK 를 클릭합니다.

- D. Add items to the Project 창이 보이면 Close 를 통해 닫습니다.

이제 유저 분은 Project 에 2개의 파일을 추가하였습니다. 그리고 그 결과는 Project 탭

을 통해서 확인할 수 있습니다.

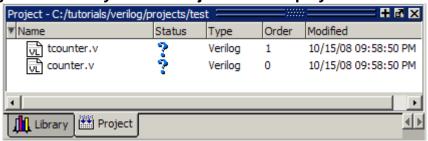

Figure 4-4. Newly Added Project Files Display a '?' for Status

## **Changing Compile Order (VHDL)**

Verilog Design 을 진행하시는 경우 이 단계를 스킵 하셔도 됩니다.

ModelSim/Questa 에서는 VHDL Design 을 vsim command 를 이용하여 loading 할 때 자동적으로 Design 정보를 모아서 Loading 이 됩니다. 하지만 VHDL Design 같은 경우에 Compile 을 할 때 순서에 맞추어 Compile 하는 것이 매우 중요합니다. (많은 파일을 가지고 Simulation 을 진행하는 경우 Order 맞추어 Compile 하는 것도 큰 작업이 됩니다.) 하지만, Project Flow 방식으로 Simulation 을 진행할 경우엔 아래의 순서대로 하시면 ModelSim/Questa 에서 자동적으로 Order 에 맞추어 Compile 이 진행됩니다.

- 1. Compile order 변경하기

- A. Compile > Compile order 를 선택합니다.

- B. Compile Order 창이 열리면 Auto Generate 를 클릭합니다.

Modelsim/Questa 에서 2개의 이상의 VHDL 파일을 Auto generate 로 Compile 을 하게 되면 우선 하나의 파일을 Compile 을 하고 나서 다른 파일을 Compile 을 하게 됩니다. 만약 Compile 을 실패하면, 해당 파일은 순서를 맨 마지막으로 이동시키고 나서 다른 파일을 Compile 하는 방법으로 Auto Generate 를 하게 됩니다.

유저 분이 직접 Compile order 를 지정할 수도 있습니다. 아래의 그림에서처럼 파일을 선택하고 화살표를 클릭해서 순서를 바꿀 수 있습니다.

Compile Order

Current Order

Vicounter.v

Counter.v

Move up/down buttons

Auto Generate OK Cancel

Figure 4-5. Compile Order Dialog Box

C. 순서를 counter, tcounter 순서로 지정하고 OK 버튼을 클릭합니다.

## **Compile the Design**

- 1. File Compile 하기

- A. Project 윈도우에서 마우스 오른쪽 버튼을 클릭하고 Compile>Compile All 을 클릭합니다.

Compile 이 아무런 문제가 없이 진행되면 Project 창에 Status 의 "?" 가 녹색 체크마 크로 변합니다. 만약 Compile 이 실패하면 빨간색 X 마크가 되고 Transcript 윈도우에 Compile 실패 메시지가 나타납니다.

- 2. Design Unit 보기

- A. Library 탭을 클릭합니다.

- B. Work library 에서 "+" 아이콘을 클릭하여 확대합니다.

확대하여 보면 Compile 된 2개의 Design unit 을 확인할 수 있습니다. 그리고 unit 에 해당하는 Source file 의 위치정보가 같이 보여집니다.

Library ₹ Name Type Path C:/tutorials/verilog/projects/work \_\_ work Library Module C:/tutorials/verilog/projects/counter.v M counter m test\_counter Module C:/tutorials/verilog/projects/tcounter.v **⊕**⊢∭ floatfixlib \$MODEL\_TECH/../floatfixlib Library Library \$MODEL\_TECH/../avm <u>∓</u>⊢ mtiOvm Library \$MODEL\_TECH/../ovm-2.0 <u>+</u>⊢ mtiUPF Library \$MODEL\_TECH/../upf\_lib ...sv\_std \$MODEL\_TECH/../sv\_std Library ±⊢ vital2000 \$MODEL\_TECH/../vital2000 Library \$MODEL\_TECH/../ieee Library \$MODEL\_TECH/../modelsim\_lib **⊥**⊢ modelsim\_lib Library Project Library

Figure 4-6. Library Window with Expanded Library

## **Optimize for Design Visibility**

- 1. vopt command 를 이용하여 Full visibility 를 갖는 Library 로 Optimize 하기.

- A. Transcript 윈도우에 아래의 command 를 입력합니다.

#### vopt +acc test\_counter -o testcounter\_opt

+acc 는 visibility 관련 옵션이며, -o 는 결과 파일 이름을 지정하는 옵션입니다.

주의 : vopt command 를 사용할 때 같은 이름으로는 결과 파일이 만들어 지지 않습니다.

## **Load the Design**

- 1. test\_counter Load 하기.

- A. 위에서 만든 Optimize design 을 vsim command 를 이용하여 load 합니다.

#### vsim testcounter\_opt

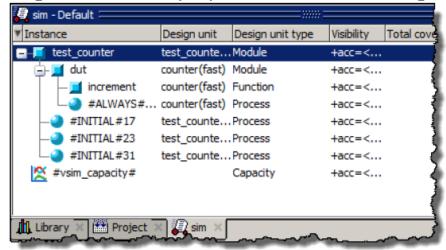

그러면, 아래의 그림과 같이 해당 Simulation 에 대한 정보를 볼 수 있습니다.

Figure 4-7. Structure(sim) window for a Loaded Design

위의 그림을 보시면 현재 진행하고 있는 Simulation 은 sim 탭에, 나타나고 Project 탭에서는 Project 에 관한 정보를 볼 수 있습니다.

#### 2. Simulation 종료하기

A. Simulate>End Simulation 을 선택하고 Yes 를 클릭합니다.

# **Organizing Projects with Folders**

만약 유저 분이 현재 진행하는 Project 에 포함되는 파일이 많은 경우엔 Project 안에 Folder 를 만들어서 계층구조로 File 을 정리, 관리할 수 있습니다. 이렇게 만들어진 Folder 실제적으로 만들어지는 디렉토리가 아니라 Project 안에서만 보여지는 Folder 입니다.

### **Adding Folders**

위에서 말한 Folder 추가를 해보겠습니다.

#### 1. 새 폴더 만들기

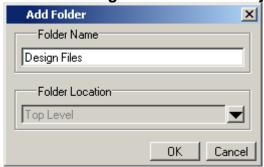

- A. Project 창에서 마우스 오른쪽 버튼을 클릭하여 Add to Project>Folder 를 선택합니다.

- B. Folder name 부분에 Design Files 라고 입력 합니다.

Figure 4-8. Adding New Folder to Project

C. 입력이 다 끝났으면 OK 를 클릭합니다.

Project 창에 Design Files 라는 이름의 Folder 가 나타납니다.

Figure 4-9. A Folder Within a Project

#### 2. Sub-Folder 만들기

- A. Project 창에서 마우스 오른쪽 버튼을 클릭하여 Add to Project>Folder 를 선택합니다.

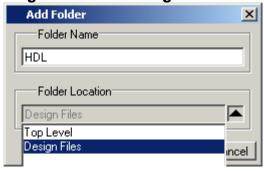

- B. Folder name 에 HDL 을 입력합니다.

Figure 4-10. Creating Subfolder

C. Folder Location 부분에 화살표를 눌러 Design Files 를 선택하고 OK 를 클릭합니다. Design Files 의 "+" 아이콘을 클릭하면 Design Files 밑에 HDL Folder 가 만들어진 것을 보실 수 있습니다.

Figure 4-11. A folder with a Sub-folder

## **Moving Files to Folders**

유저 분은 위에서 Folder 를 만들었습니다. 그럼 이제 실제로 Folder 에 파일들을 이동 해보겠습니다.

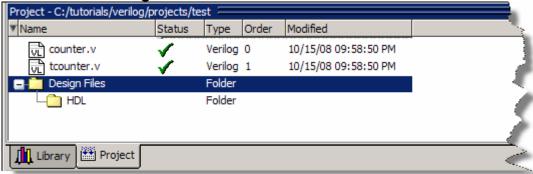

- 1. HDL 폴더로 파일 이동시키기

- A. Project 윈도우에서 2개의 파일을 전부 선택합니다.

- B. 파일을 선택했으면 마우스 오른쪽 버튼을 클릭하고 Properties 클릭합니다.

- C. Place in Folder 를 클릭하고 HDL 폴더를 선택합니다.

- D. 선택이 끝났으면 OK 버튼을 클릭합니다.

Figure 4-12. Changing File Location

"+" 아이콘을 클릭하시면 Design File 밑에 HDL 폴더가 있고 HDL 폴더 안에 Design 파일들이 추가된 것을 볼 수 있습니다.

Project 윈도우 상에 Status 가 "?" 로 변경이 되어 있을 겁니다. 이것은 파일이 이동이 되었기 때문에 현재 상태를 알지 못하기 때문에 "?" 로 표시되는 것입니다.

# **Using Simulation Configurations**

Simulation configuration 은 Simulation 을 진행하는 필요한 option 들이 모여 있습니다. 예를 들어 어떤 Design 을 Simulation 을 하는데 resolution time, Hazard option 등을 체크하여 Simulation 을 진행하였다면, 여러분은 Resolution time 과 Hazard 2개의 Simulation Configuration 을 이용하여 Simulation 을 진행한 것입니다. Project Flow 방식으로 진행하면 이런 Simulation configuration 을 따로 저장하여 더블 클릭 하는 것만으로 자동적으로 해당 Option 에 맞추어 Simulation 을 진행할 수 있습니다.

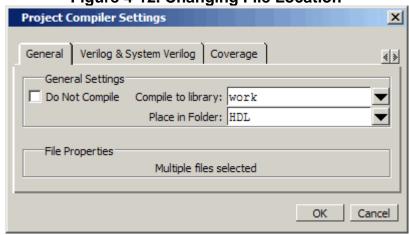

- 1. 새로운 Simulation Configuration 만들기

- A. Project 윈도우에서 마우스 오른쪽 버튼을 눌러 나오는 팝업 메뉴에서 Add to Project>Simulation configuration 을 선택합니다.

Figure 4-13. Simulation Configuration Dialog Box Add Simulation Configuration X Simulation Configuration Name Place in Folder HDL Add Folder... counter Design VHDL Verilog Libraries SDF Others ∢ > ▼ Name Path Туре ⊒**⊣∭** work Library C:/questasim\_6.5d/examples/tutorials... → M counter Module C:/questasim\_6.5d/examples/tutorials... — ₩ test\_counter Module C:/questasim\_6.5d/examples/tutorials... testcounter\_opt...Optimized... **⊕-∭** floatfixlib Library \$MODEL\_TECH/../floatfixlib Library \$MODEL\_TECH/../avm \$MODEL\_TECH/../ovm-2.0.3 Library Library \$MODEL\_TECH/../pa\_lib **⊕⊣∭** mtiUPF \$MODEL\_TECH/../upf\_lib Library \$MODEL\_TECH/../sv\_std **∓⊣∭** sv\_std Library Design Unit(s): Resolution ▼ work.test\_counter pз Optimization Enable optimization Optimization Options. Save Cancel

- B. Simulation Configuration Name 부분에 counter 이라고 입력합니다.

- C. Place in Folder 부분을 클릭하여 HDL 로 선택합니다.

- D. Design 탭에서 Work 앞의 "+" 아이콘을 클릭하여 test\_conter 를 선택합니다.

- E. Resolution time 을 ps 로 설정합니다.

- F. Enable optimization 부분의 체크를 해제합니다.

- G. Verilog 를 사용하는 유저는 Verilog 탭을 선택하여 Enable hazard checking 을 합니다.

VHDL 유저는 진행을 안 하셔도 됩니다.

- H. Save 버튼을 클릭합니다. 그러면 Project 윈도우 HDL 폴더 밑에 counter 라는 이름의 Simulation Configuration 이 만들어 집니다.

- I. 이제 Status 가 "?" 로 표시된 파일들을 Compile 하겠습니다.

Project 창에서 2개의 파일을 전부 선택합니다.

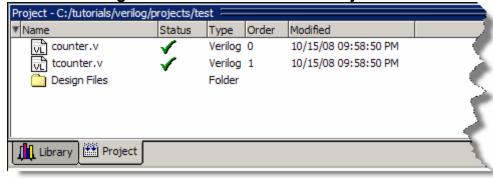

J. Compile>Compile All 을 선택하면 해당 파일이 Compile 이 되고 아래와 같이 Status 가 녹색 체크로 변하게 됩니다.

Project - C:/tutorials/verilog/projects/test Order Modified ₹ Name Status Type Design Files Folder Folder 10/15/08 09:58:50 PM Verilog tcounter.v 1 10/15/08 09:58:50 PM Simulation Library Project

Figure 4-14. A Simulation Configuration in the Project window

- 2. Simulation Configuration Load 하기

- A. 위의 단계에서 만들어 놓은 Simulation Configuration 인 counter 를 더블 클릭합니다.

위의 Simulation Configuration 을 실행하면 Transcript 윈도우에는 해당하는 Option 들이 command 로 변경되어 보여집니다.

Figure 4-15. Transcript Shows Options for Simulation Configurations

```

Transcript

vsim -hazards -t ps -novopt work.test_counter

# vsim -hazards -t ps -novopt work.test_counter

# Loading work.test_counter

# Loading work.counter

Command Line

Switches

VSIM 14>]

Project: test Now: 0 ps

```

#### 3. Simulation 종료하기

- A. Simulate>End Simulation 을 선택하면 현재 진행중인 Simulation 이 종료 됩니다.

- B. Project 윈도우에서 마우스 오른쪽 버튼을 클릭하여 Close Project 를 선택하여 Project 를 종료합니다.

# **Chapter 5 Working With Multiple Libraries**

이번 챕터에서는 Multiple library 를 이용하여 Simulation 하는 방법을 연습해 볼 것입니다. 여러분들은 Design 을 Simulation 하기 위해 특정 third-party 의 IP, 혹은 다른 Library 등과 연계하여 Simulation 을 할 수도 있습니다.

그런 경우에 대비하여 Resource library 를 만들고 자신의 Design 와 연동하여 Simulation 을 하는 것에 대해 살펴볼 것입니다.

이 챕터에서 예제 파일을 가지고 작업을 진행할 것입니다. 챕터의 예제 파일은 8bit binary up counter 이며 해당 파일은 ModelSim/Questa 를 설치된 경로 안에 있습니다.

**Verilog** — <install\_dir>/examples/tutorials/verilog/libraries/counter.v and tcounter.v **VHDL** — <install\_dir>/examples/tutorials/vhdl/ libraries /counter.vhd and tcounter.vhd

예제 파일들은 Verilog 와 VHDL 둘 다 지원을 하고 있습니다. 가지고 계신 ModelSim/Questa 의 License 에 따라 해당하는 언어 예제를 선택하시면 됩니다.

### **Creating the Resource Library**

Resource library 를 만들기 전에 여러분은 ModelSim/Questa 가 설치된 디렉토리에 있는 modelsim.ini 파일을 읽기 전용으로 만들어 주어야 합니다. 읽기 전용으로 변경하셨으면 이제 아래의 절차에 따라 진행해 주시기 바랍니다.

1. Resource library 를 위한 디렉토리 만들기

resource library 라는 이름으로 새로운 디렉토리를 만들고 <install\_dir>/examples/tutorials/verilog/libraries 디렉토리에서 counter 파일을 copy 합니다.

2. Test bench 를 위한 디렉토리 만들기

이제는 Test bench 를 위한 디렉토리를 만들 것입니다. testbench 라는 디렉토리를 만들고 <install\_dir>/examples/tutorials/verilog/libraries 디렉토리에서 tcounter 파일을 copy 합니다.

이제 유저 분은 이번 챕터에서 2개의 디렉토리를 만들었습니다.

- 3. 이제 ModelSim/Questa 를 실행하고 Change Directory 를 resource library 로 지정합니다.

- A. 만약 지난 챕터를 이어서 바로 시작하시는 경우엔 ModelSim/Questa 가 구동 되어 있으니 다시 실행할 필요가 없습니다.

단축 아이콘을 클릭하거나 vsim command 를 입력하면 ModelSim/Questa 의 GUI 가 올라옵니다.

- B. File>Change Directory 에서 위에서 만든 디렉토리로 지정합니다.

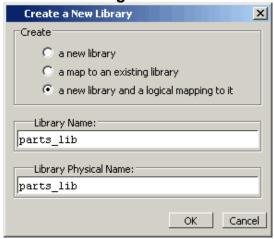

- 4. Resource library 만들기

- A. File>New>Library 를 선택합니다.

- B. Library name 부분에 parst\_lib 을 입력합니다.

Figure 5-1. Creating New Resource Library

Library name 부분을 입력하면 자동적으로 Library Physical Name 부분도 채워집니다. 위와 같이 입력이 되었으면 OK 를 클릭합니다.

5. Resource Library 에 counter 파일 Compile 하기

- A. 메인 메뉴의 Compile 아이콘을 클릭합니다.

- B. Library 부분의 화살표를 클릭하여 parts\_lib 을 선택합니다.

Compile Source Files

Library: parts\_lib

Look in: resource\_library

parts\_lib

counter.v

File name: counter.v

Compile

Done

Edit Source

Figure 5-2. Compiling into the Resource Library

C. counter.v 파일을 선택하고 더블 클릭을 하거나 Compile 버튼을 클릭합니다.

Default Options...

Files of type: HDL Files (\*,v;\*,vl;\*,vhd;\*,vhd;\*,vho;\*,hdl;\*,v ▼

Compile selected files together

- D. Done 버튼을 클릭합니다.

- 6. 디렉토리를 test bench 로 변경하기

- A. File>Change Directory 를 선택하고 test bench 디렉토리를 선택합니다.

# **Creating the Project**

Counter 의 test bench 를 위한 Project 만들기

- 1. 프로젝트 만들기

- A. File>New>Project 를 선택합니다.

- B. Project name 부분을 counter 로 선택합니다.

- C. Project Location 혹은 Default library name 부분은 변경하지 않습니다.

- D. OK 를 선택합니다.

- 2. Project 에 test bench 추가하기

- A. Add Existing File 을 선택합니다.

- B. Browse 버튼을 클릭하고 tcounter.v 파일을 추가합니다.

- 3. Compile 하기

- A. tcounter.v 파일을 선택하고 마우스 오른쪽 버튼을 클릭한 후 Compile>Compile

Selected 를 선택합니다.

## **Loading Without Linking Libraries**

지금 과정에서는 이전에서 만들어 놓은 parts\_lib library 를 link 를 걸어서 Simulation 을 진행해 볼 것입니다. 이 과정은 Verilog 과 VHDL 이 진행과정이 서로 다릅니다.

#### **Verilog**

#### **Optimize the Verilog Design for Debug Visibility**

- 1. vopt 를 이용하여 full visibility 를 가지는 optimize design 만들기

- A. Transcript 윈도우에서 다음과 같이 command 를 입력합니다.

vopt +acc test\_counter -o testcounter\_opt

B. quit -sim 을 입력합니다.

#### **VHDL**

#### **Optimize the VHDL Design for Debug Visibility**

- 1. vopt 를 이용하여 full visibility 를 가지는 optimize design 만들기

- A. Transcript 윈도우에서 다음과 같이 command 를 입력합니다.

vopt +acc test counter -o testcounter opt

위와 같이 command 를 입력하면 아래와 같은 3473 Warning 메시지를 보게 될 것입니다. 이 메시지는 dut counter 에 대한 정보를 읽어오지 못해 발생하는 메시지 입니다.

Figure 5-4. VHDL Simulation Warning Reported in Main Window

B. verror 3473 이라고 입력합니다.

verror 은 warning, error 메시지에 대해 좀더 자세한 정보를 보기 원할 때 사용되는 command 입니다.

C. quit -sim 을 입력합니다.

### **Linking to the Resource Library**

유저 분이 특정한 Library 를 Link 를 걸어서 Simulation 을 진행하려는 경우엔 search library 라는 옵션을 사용하여 Simulator 를 동작시켜야 합니다.

1. Simulation 을 진행하면서 특정한 library 찾기

- A. 메인 메뉴에서 Simulate 아이콘을 클릭하거나 Simulate > Simulate 를 클릭합니다.

- B. work library 에서 "+" 아이콘을 클릭하여 test\_counter 를 선택합니다.

- C. Enable optimization 체크 박스 의 체크를 해제합니다.

- D. Library 탭을 선택합니다.

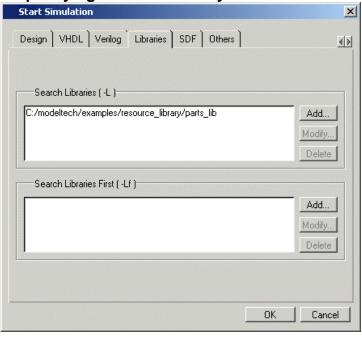

- E. Search Library 에서 Add 버튼을 클릭하여 resource library 에 parts\_lib 을 선택하고 OK 를 클릭합니다.

아래의 그림처럼 Library 가 추가된 것을 확인할 수 있습니다.

Figure 5-5. Specifying a Search Library in the Simulate Dialog Box

F. OK 버튼을 클릭합니다.

# **Permanently Mapping VHDL Resource Libraries**

위에서와 같이 VHDL Design 을 Simulation 을 진행하려고 할 때마다 Library 를 추가해서 작업을 하면 유저 분은 상당히 많은 불편을 감수하면서 Project 마다 Link 를 걸어주어야 합니다. 하지만 ModelSim/Questa 환경 설정 파일인 modelsim.ini 파일을 수정하시면 그런 불편 없이 사용이 가능합니다.

- 1. ModelSim/Questa 가 설치된 디렉토리로 이동합니다.

- 2. 만약을 대비해 반드시 Backup 파일을 만들어 둡니다.

- 3. Modelsim.ini 파일의 읽기전용을 해제합니다.

- 4. 파일을 워드 패드를 이용해 Open 합니다.

[Library] 부분에 위에서 만들었던 parts\_lib 을 등록합니다.

Ex) parts\_lib = c:/libraries/parts\_lib

- 5. 파일을 저장합니다.

- 6. 저장한 파일을 읽기 전용파일로 변경합니다.

- 7. Simulation 종료하기

- A. Simulate>End Simulation 을 선택하면 현재 진행중인 Simulation 이 종료 됩니다.

# **Simulating SystemC Designs**

ModelSim/Questa 에서는 SystemC 로 설계된 Design 역시 Simulation 을 진행할 수 있습니다. HDL Design 과 마찬가지로 Simulation 과 Debugging 환경을 제공합니다.

이번 챕터에서는 먼저 SystemC 로 만들어진 아주 간단한 Basic 이라는 Design 을 Simulation 할 것입니다. 그 다음엔 HDL 과 SystemC 로 구현되어 있는 ring buffer 를 가지고 Simulation을 진행할 것입니다. 예제 파일의 위치는 다음과 같습니다.

**SystemC** – <install\_dir>/examples/systemc/sc\_basic

**SystemC/Verilog** – <install\_dir>/examples/systemc/sc\_vlog

**SystemC/VHDL** – <install\_dir>/examples/systemc/sc\_vhdl

### **Setting up the Environment**

SystemC 를 사용하기 위해서는 SystemC 관련 License 가 있어야 합니다. 만약 SystemC 관련 License 가 없으시다면 이번 챕터는 진행할 수 없습니다. 또한 SystemC 를 사용하기 위해서는 다음 표에서 보여지는 Platform 별 C Compiler 가 필요합니다.

Table 6-1. Supported Platforms for SystemC

| Platform/OS                                                                                                                                          | Supported compiler versions                                                                               | 32-bit support | 64-bit<br>support |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------|-------------------|

| Intel and AMD x86-based<br>architectures (32- and<br>64-bit)<br>SUSE Linux Enterprise<br>Server 9.0, 9.1, 10, 11<br>Red Hat Enterprise Linux 3, 4, 5 | gcc 4.0.2, gcc 4.1.2, gcc 4.3.3<br>VCO is linux (32-bit binary)<br>VCO is linux_x86_64 (64-bit<br>binary) | yes            | yes               |

| Solaris 8, 9, and 10                                                                                                                                 | gcc 4.1.2                                                                                                 | yes            | no                |

| Solaris 10 on x86                                                                                                                                    | gcc 4.1.2                                                                                                 | yes            | yes               |

| Windows XP <sup>1</sup> , Vista and 7                                                                                                                | Minimalist GNU for Windows (MinGW) gcc 4.2.1                                                              | yes            | no                |

1. SystemC supported on this platform with gcc-4.2.1-mingw32vc9.

보다 자세한 정보는 User Manual 의 SystemC 관련 부분을 살펴보시기 바랍니다.

### Preparing an OSCI SystemC Design

Open SystemC Initiative – OSCI 와 호환되는 SystemC Design 을 Simulation 을 하기 위해서는 아래의 사항을 체크해 주셔야 합니다.

- sc main() 으로 선언되어 있는 함수를 sc module() 로 변경합니다

- sc\_initialize() 는 삭제합니다.

- 최상위 module 은 sc\_module\_export 를 사용합니다.

- 1. 디렉토리 만들고 예제 파일 복사하기

새로운 디렉토리를 만들고 *<install\_dir>/examples/systemc/sc\_basic* 디렉토리에서 파일을 새로운 디렉토리로 파일을 복사합니다.

- 2. 이제 ModelSim/Questa 를 실행하고 Change Directory 를 resource library 로 지정합니다.

- A. 만약 지난 챕터를 이어서 바로 시작하시는 경우엔 ModelSim/Questa 가 구동 되어있으니 다시 실행할 필요가 없습니다.

단축 아이콘을 클릭하거나 vsim command 를 입력하면 ModelSim/Questa 의 GUI 가 올라옵니다

- B. File>Change Directory 에서 위에서 만든 디렉토리로 지정합니다.

- 3. 메인 메뉴의 File>Open 를 선택하여 ModelSim/Questa 에서 제공하는 Text editor 를 이용 해 basic\_orig.cpp 파일을 엽니다.

- A. 파일은 읽기 전용일 것입니다. Source 윈도우에서 마우스 오른쪽 버튼을 클릭하여 읽 기전용을 해제합니다.

- B. 아래의 그림처럼 파일을 수정합니다.

Ln# 9 // basic.cpp (modified file) • 10 #include "basic.h" 11 12 #ifdef MTI\_SYSTEMC 13 Add this 14 SC\_MODULE\_EXPORT(top); 15 preprosessor 16 directive. 17 #else 18 int sc\_main( int, char\*[] ) 19 20 申 { sc\_clock clk; 21 22 mod\_a a( "a" ); 23 24 a.clk( clk ); 25 26 sc\_initialize(); 27 return 0; 28 29 - } 30

Figure 6-1. The SystemC File After Modifications

C. 파일을 저장합니다.

31

수정한 파일은 sc\_basic/gold 디렉토리에 있으니 복사해서 사용해도 됩니다.

- 1. basic\_orig.h 파일 수정하기

- A. 파일은 읽기 전용일 것입니다. Source 윈도우에서 마우스 오른쪽 버튼을 클릭하여 읽기 전용을 해제합니다.

- B. 그리고 아래의 그림처럼 수정합니다.

#endif

Figure 6-2. Editing the SystemC Header File.

```

SC_METHOD( main_action_method );

46

SC_THREAD( main_action_thread );

47

48

SC CTHREAD( main action cthread, clk.pos() );

49

50

- };

51

#ifdef MTI SYSTEMC

52

Add this

53

SC_MODULE(top)

54

preprocessor

55

sc_clock clk;

directive.

56

mod_a a;

57

58

SC CTOR (top)

: clk("clk", 200, SC_NS, 0.5, 0.0, SC_NS, false),

59

60

a("a")

61

62

a.clk( clk );

63

64

65

#endif

```

C. basic.h 로 파일을 저장합니다. 이 파일 역시 /sc\_basic/gold 에 있는 파일을 카피해서 사용해도 됩니다.

이제 Simulation 을 하기 위한 파일 수정이 끝났습니다.

# Compiling a SystemC-only Design

파일 수정이 끝났으면 이제는 파일들을 Compile 해야 합니다. ModelSim/Questa 에서는 sccom command 를 이용하여 compile 할 수 있습니다.

- 1. Work library 만들기

- A. Transcript 윈도우에 vlib work 라고 입력합니다.

- 2. SystemC 파일 Compile 하고 Link 하기

- A. 계속해서 아래의 command 를 입력합니다.

#### sscom -g basic.cpp

B. 컴파일이 끝났으면 SystemC object 와 link 를 걸어야 합니다. 아래의 command 를 입력합니다.

sccom - link

이제 Compile 과 link 가 성공적으로 마무리 되었습니다. 이제 다음 단계에서는 SystemC 와 HDL 이 Mix 되어 있는 Design 에 대해 진행을 할 것입니다.

### Mixed SystemC and HDL Example

이제 여러분은 HDL Instant 를 가지고 있는 SystemC Design 을 가지고 작업을 진행할 것입니다,

1. 새로운 디렉토리 만들고 파일 복사하기

새로운 디렉토리를 만들고  $<install\_dir>/examples/systemc/sc\_vlog$  디렉토리에서 파일을 새로운 디렉토리로 파일을 복사합니다.

VHDL 을 사용하시는 분은 *install\_dir>/examples/systemc/sc\_vhdl* 의 파일을 새로운 디렉토리로 카피합니다.

- 2. 이제 ModelSim/Questa 를 실행하고 Change Directory 를 resource library 로 지정합니다.

- A. 만약 지난 챕터를 이어서 바로 시작하시는 경우엔 ModelSim/Questa 가 구동 되어 있으니 다시 실행할 필요가 없습니다.

단축 아이콘을 클릭하거나 vsim command 를 입력하면 ModelSim/Questa 의 GUI 가 올라옵니다

- B. File>Change Directory 를 통해 위에서 만든 디렉토리로 지정합니다.

- 3. Work library 만들기

- A. Transcript 윈도우에 vlib work 를 입력합니다.

- 4. Compile 하기

- A. Verilog

Transcript 윈도우에 vlog \*.v 를 입력합니다.

B. VHDL

Transcript 윈도우에 vcom -93 \*.vhd 를 입력합니다.

5. Verilog ringbuf 모듈을 위해 외부 모듈 선언하기

#### A. Verilog

Transcript 윈도우에 **scgenmod -map "scalar=bool" ringbuf>ringbuf..h** 를 입력합니다. -map "scalar=bool" 옵션은 외부 포트를 내부 논리값으로 사용하기 위해 사용됩니다.

B. VHDL

scgenmod ringbuf<ringbuf.h 를 입력합니다.

이제 ringbuf.h 파일을 열어보면 다음과 같습니다.

Figure 6-3. The ringbuf.h File.

```

+ d ×

C:/examples/systemc/sc_vlog/ringbuf.h - Default

Ln#

1

#ifndef _SCGENMOD_ringbuf_

٠

2

#define SCGENMOD ringbuf

3

4

#include "systemc.h"

5

6

class ringbuf : public sc foreign module

₽ {

7

8

public:

9

sc in<bool> clock;

10

sc_in<bool> reset;

sc_in<bool> txda;

11

sc_out<bool> rxda;

12

13

sc_out<bool> txc;

14

sc out<bool> outstrobe;

15

16

17

ringbuf(sc_module_name nm, const char* hdl_name,

18

int num_generics, const char** generic_list)

19

: sc_foreign_module(nm),

20

clock("clock"),

21

reset ("reset"),

22

txda ("txda"),

23

rxda("rxda"),

24

txc("txc"),

25

outstrobe ("outstrobe")

26

{

27

elaborate foreign module (hdl name, num generics, generic list);

28

29

~ringbuf()

30

{ }

31

32

- };

33

34

- #endif

```

Test\_ringbuf.cpp 파일을 보면 아래와 같이 test\_ringbuf.h 파일을 포함하고 있는 것을 볼 수 있습니다.

Figure 6-4. The test\_ringbuf.cpp File

```

C:/examples/systemc/sc_vlog/test_ringbuf.cpp - Default

+ \sim

Ln#

•

8

9

// test_ringbuf.cpp

10

#include "test ringbuf.h"

12

#include <iostream>

13

14

15

SC_MODULE_EXPORT(test_ringbuf);

16

```

- 6. SystemC 파일 Compile 하고 Link 걸기

- A. Transcript 윈도우에 sccom -g test\_ringbuf.cpp 를 입력합니다.

- B. Transcript 윈도우에 sccom -link 를 입력합니다.

- 7. Full visibility optimize design 만들기

- A. Transcript 윈도우에 vopt +acc test\_ringbuf -o test\_ringbuf\_opt 를 입력합니다,

- 8. 디자인 Load 하기

- A. Transcript 윈도우에 vsim test\_ringbuf\_opt 를 입력합니다.

디자인이 로드가 되면서 Process 윈도우나 Objects 윈도우가 열릴 것 입니다. 해당 윈도우는 메인 메뉴의 View 메뉴를 통해서 새로운 윈도우를 열거나 닫을 수 있습니다.

+ A × 📳 sim - Default 🛭 🔷 Objects 🗉 -------크보레× ₹ Name ▼ Instance Design unit Design unit type Value Kind Mode test\_ringbuf ScModule - test\_ringbuf ScVariable Internal counter ringbuf(fast) Module reset\_deacti... INACTIVE 🛓 - 🗾 ring\_INST ScEvent Internal true 10 0.5...ScPrimC...Internal **■** dock reset\_generator...test\_ringbuf ScMethod reset generate\_data test\_ringbuf ScMethod compare\_data test\_ringbuf ScMethod txda ScPrimC...Internal print\_error test ringbuf ScMethod ScPrimC...Internal 🔷 txc print\_restore test ringbuf ScMethod ScPrimC...Internal #vsim\_capacity# 🔷 outstrobe ScPrimC...Internal Capacity + pseudo 000000000...ScPrimC...Internal + storage 000000000...ScPrimC...Internal false ScPrimC...Internal Sim × < ▶</p> Library Project 🤼 Capacity dataerror false ScPrimC...Internal false ScPrimC...Internal actual H M X Transcript • # Loading work.ringbuf(fast) # Loading work.control(fast) # Loading work.store(fast) # Loading work.retrieve(fast) VSIM 15>

Figure 6-5. The test\_ringbuf Design

## Viewing SystemC Objects in the GUI

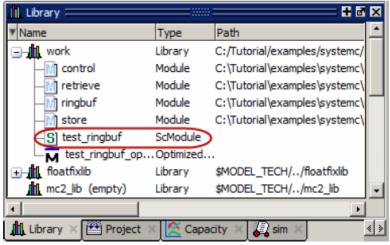

SystemC 의 Design Object 들은 ModelSim/Questa 의 GUI 상에 녹색 아이콘으로 표시됩니다. 그리고 Object 의 종류에 따라 해당 아이콘이 사각형, 원 혹은 다이아몬드 형태로 표시됩니다.

- 1. Library 윈도우에서 Objects 보기

- A. Library 윈도우에서 work library 앞의 "+" 아이콘을 클릭하여 펼칩니다. SystemC Object 는 녹색 S 마크로 표현됩니다.

Figure 6-6. SystemC Objects in the work Library

- 2. Wave 윈도우에 Object 추가하기

- A. Structure 윈도우(sim) 에서 test\_ringbuf 를 선택하고 마우스 오른쪽 버튼을 클릭하여 Add>To wave>All items in region 을 선택합니다.

# **Setting Breakpoints and Stepping in the Source Window**

Source 윈도우를 통해 HDL 에서 breakpoint 를 설정한 것과 마찬가지로 SystemC 파일에서도 Breakpoint 를 설정할 수 있습니다. ModelSim/Questa 의 C debug 기능을 통해 작업이 이루어 집니다. C Debug 에 대해서는 유저 매뉴얼에서 C Debug 부분을 살펴보시면 더욱 자세히 알 수 있습니다.

- 1. C Debug 를 이용하여 breakpoint 를 사용하기 위해서는 ModelSim/Questa 의 설정을 변경 해 주셔야 합니다.

- A. Tools>C Debug>Allow lib step 혹은 Enable auto step 을 선택합니다.

- 2. Breakpoint 설정하기

- A. Structure (sim) 탭에서 test\_ringbuf 를 선택하여 Source 윈도우에 Open 합니다.

- B. Source 윈도우에서 VHDL, Verilog 상관 없이 150번 line 으로 이동합니다.

- C. 아래의 이미지에서 보이는 것처럼 해당 line 에 breakpoint 를 설정합니다.

Verilog : bool var\_dataerror\_newval = actual.read()...

VHDL : sc\_logic var dataerror newval = actual.read ...

Figure 6-7. Active Breakpoint in a SystemC File

```

C:/tutorials/systemc/sc_vlog/test_ringbuf.h

Ln#

147

// On every negedge of the clock, compare actual and expected da

148

149

inline void test ringbuf::compare data()

150

1510

bool var dataerror newval = actual.read() ^ !expected.read()

dataerror.write(var dataerror newval);

152

153

154

if (reset.read() == 0)

155

156

storage.write(0);

157

expected.write(0);

Wave

C] test_ringbuf.h

```

- 3. Simulation 동작 하기

- A. run 500 을 입력합니다.

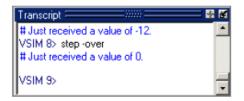

Simulation 이 진행을 하시면, 기존의 breakpoint 설정하셨던 거와 마찬가지고 해당 Source 윈도우에서 해당 line 에 화살표가 표시되면서 Simulation 이 멈추어지며 아래의 메시지가 Transcript 윈도우에 표시됩니다.

```

# C breakpoint c.1

# test_ringbuf::compare_data (this=0x27c4d08) at test_ringbuf.h:151

```

Figure 6-8. Simulation Stopped at Breakpoint

```

C:/tutorials/systemc/sc_vlog/test_ringbuf.h =

Ln#

147

// On every negedge of the clock, compare actual and expected da

148

149

inline void test ringbuf::compare data()

150

151

bool var_dataerror_newval = actual.read() ^ !expected.read()

152

dataerror.write(var_dataerror_newval);

153

154

if (reset.read() == 0)

155

156

storage.write(0);

157

expected.write(0);

Wave C test_ringbuf.h

```

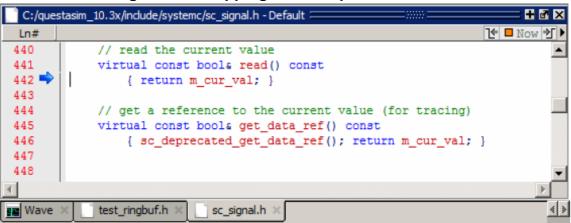

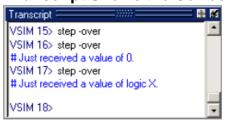

B. 메인 메뉴에서 step 아이콘을 클릭합니다. 해당 아이콘을 클릭하면 다음 Statement 도 이동을 합니다. 다음 Statement 는 파일과는 상관없이 Simulation 을 진행되어 가는 동안에 발생하는

Function 에 따로 동작하게 됩니다. 아래의 이미지처럼 sc\_signal.h 파일의 440 번 line으로 이동됩니다.

Figure 6-9. Stepping into a Separate File

C. Continue run 아이콘을 클릭하면 다시 simulation 이 진행되며 breakpoint 에서 동작이 멈추어 집니다.

#### **Examining SystemC Objects and Variables**

SystemC 의 Object 의 value 는 Object 윈도우에서 볼 수 있습니다. 그리고 examine 라는 command 를 입력해서도 볼 수 있습니다.

- 1. sc\_signal 의 type 과 value 보기

- A. CDBG 프롬프트 상태에서 show 를 입력하면, Transcript 윈도우에 Design 의 Object 들의 Type 과 Value 가 보여집니다.

Figure 6-10. Output of show Command

```

CDBG 15> show

# ptype this

# type = class test_ringbuf : public sc_core::sc_module {

# public:

sc_core::sc_dock dock;

sc_core::sc_event reset_deactivation_event;

sc_core::sc_signal<bool> reset;

sc_core::sc_signal<bool> txda;

sc_core::sc_signal<bool> rxda;

sc_core::sc_signal<bool> txc;

sc_core::sc_signal < bool > outstrobe;

sc_core::sc_signal<sc_dt::sc_uint<20>> pseudo;

sc_core::sc_signal<sc_dt::sc_uint<20>> storage;

sc_core::sc_signal < bool > expected;

sc_core::sc_signal<bool> dataerror;

sc_core::sc_signal<bool> actual;

int counter;

ringbuf *ring_INST;

void reset_generator();

void generate_data();

void compare_data();

void print_error();

void print_restore();

test_ringbuf(sc_core::sc_module_name);

# ~test_ringbuf(int);

# } * const

# ptype var_dataerror_newval

# type = bool

CDBG 16>

Now: 10 ns Delta: 1

sim:/test_ringbuf/compare_data/

```

B. examine dataerror 를 입력합니다.

True 라는 메시지가 출력됩니다.

- 2. SystemC variable Value 보기

- A. 위에서와 마찬가지로 examine counter 를 입력합니다.

"32'hFFFFFFF" 라는 value 가 메시지로 표시됩니다.

#### Removing a Breakpoint

- 1. Source 윈도우로 들어가 열려있는 test\_ringbuf.h 파일에 설정된 breakpoint 를 제거하기

- A. 440 line 에서 마우스 오른쪽 버튼을 클릭하여 remove breakpoint 를 설정합니다.

- 2. Simulation 구동하기

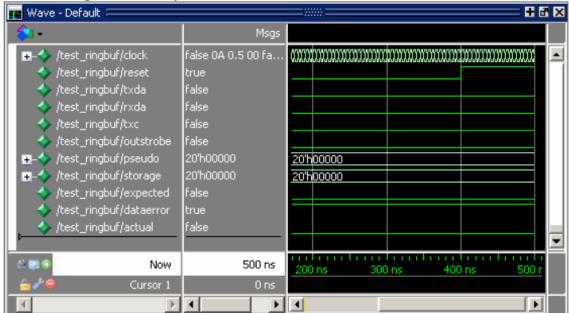

- A. run 500ns 를 입력하고 wave 윈도우에서 파형을 살펴봅니다.

Figure 6-11. SystemC Primitive Channels in the Wave Window

#### 3. C debugger 종료하기

A. Tool>C Debug > Quit C Debug 을 선택하면 현재 진행중인 C debugger 가 종료 됩니다.

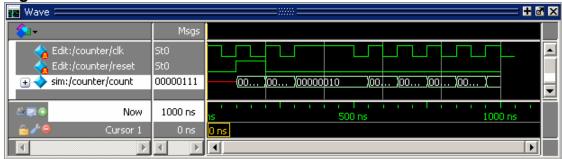

# **Chapter 7 Analyzing Waveforms**

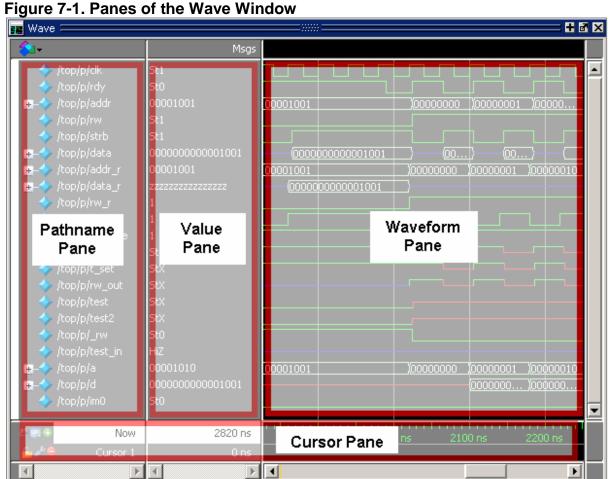

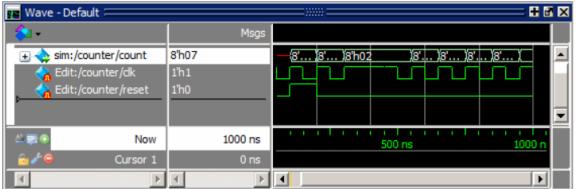

Simulation 결과는 Wave 윈도우에서 확인 할 수 있습니다. Wave 윈도우는 3개의 작은 창으로 구성되어 있습니다. Signal 이름을 보는 Pathname pane, Value 를 확인하는 Value pane, 마지막으로 파형이 보여지는 Waveform pane 입니다. 이 3개의 Pane 은 유저가 원하는 사이즈로 resize 가 가능합니다.

Loading a Design

이번에 사용할 Design 을 기존 Basic Simulation 에서 사용했던 Design 을 가지고 진행을 할 것입니다.

1. 이전 Chapter 를 진행하시고 ModelSim/Questa 를 종료를 안 했다면, 이어서 하면 되고, 만약 종료하셨으면, Tool 를 새로 동작시킵니다.

- A. 단축 아이콘을 더블 클릭하거나, vsim 을 입력합니다.

- 2. 디자인 load 하기

- A. File>Change Directory 에서 기존 Basic Simulation 에서 사용했던 디렉토리를 지정합니다.

- B. 디렉토리를 지정하면 이전에 챕터를 진행하면서 만들어 놓았던 work library 가 올라와 있는 것을 볼 수 있습니다.

- C. 기존 챕터를 진행을 하며 만들어 놓았던 optimize design 을 load 합니다.

vsim testcounter\_opt

#### Add Objects to the Wave Window

ModelSim/Questa 에서는 Wave 윈도우로 Object 를 추가하는 여러 가지 방법들이 있습니다. 이 번에는 그 방법들을 하나 하나씩 연습해 보겠습니다.

- 1. Object 윈도우로부터 Object 추가하기

- A. View>Object 를 선택하여 Object 윈도우를 엽니다.

- B. Object 윈도우에서 한 Object 를 선택하고, 마우스 오른쪽을 클릭하여 Add>To Wave>Signals in Region 를 선택합니다.

Wave 윈도우가 열리면서 Wave 윈도우에 선택한 Signal 과 같은 region 에 있는 signal 들이 보여집니다.

2. Wave 윈도우 외부로 독립시키기

일반적으로 ModelSim/Questa 에서 Wave 윈도우는 메인 윈도우 안에서 하나의 창으로 열립니다. 하지만 외부로 창을 독립시켜 단독 윈도우로 사용하는 것도 가능합니다. 기본설정역시 변경하는 것이 가능합니다. 기본 설정 변경은 유저 매뉴얼에서 Simulator GUI Preference 를 참조하시면 됩니다.

A. Wave 윈도우 오른쪽 상단의 아이콘 중에 undock 아이콘을 클릭합니다. 아이콘을 클릭하면 Wave 윈도우는 독립된 창으로 열립니다.

3. Drag and Drop 을 통해서 Object 추가하기

ModelSim/Questa 의 여러 윈도우-Structure, Objects ad Locals-에서 Drag and Drop 을 통해서 Signal 을 추가할 수 있습니다.

- A. Wave 윈도우에서 Eidt>Select All 을 선택하고 Edit>Delete 를 선택하여 모든 signal 을 삭제합니다.

- B. Work space 윈도우의 Structure(sim) 탭에서 instance 를 선택하고 drag and drop 으로 wave 윈도우에 추가합니다.

- C. Wave 윈도우에서 Eidt>Select All 을 선택하고 Edit>Delete 를 선택하여 모든 signal 을 삭제합니다.

- 4. add wave command 사용하여 추가하기

- A. Transcript 윈도우에 add wave \* 를 입력합니다.

- B. Run 500ns 를 입력하고 wave 윈도우에서 파형을 봅니다.

# **Zooming the Waveform Display**

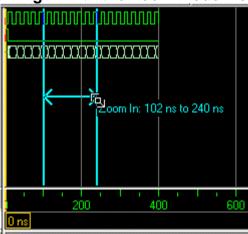

Wave 윈도우의 파형을 줌-인/줌-아웃 하는 여러 가지 방법에 대해 알아보겠습니다.

- 1. zoom 하는 여러 가지 방법 알아보기

- A. wave 윈도우에서 zoom 아이콘을 클릭합니다.

B. wave 윈도우의 파형 부분에서 마우스를 클릭하고 오른쪽 아래방향으로 드래그 합니다. 그러면 아래의 이미지처럼 확대가 됩니다.

Figure 7-2. Zooming in with the Zoom Mode Mouse Pointer

C. View>Zoom>Zoom Last 를 클릭합니다.

그러면 화면은 이전의 zoom 전의 화면으로 전환 됩니다.

D. Zoom In 아이콘을 클릭합니다.

E. View>Zoom>Zoom Full 을 클릭합니다.

### **Using Cursors in the Wave Window**

유저 분은 Wave window 에서 Cursor 를 이용하여 mark 할 수 있습니다. Wave Window 를 처음 열면 Cursor 는 기본적으로 time 0 에 위치하고 있습니다. 그 뒤에 Wave Window 에서 마우스 클릭하면 해당 커서가 클릭한 위치로 이동을 하게 됩니다.

#### 유저 분은 또한,

Cursor 를 여러 개 추가할 수 있습니다.

Cursor 가 움직이지 않게 Lock 을 하거나 지울 수도 있습니다.

Cursor 간의 interval 간격을 볼 수 있습니다.

Cursor 를 이용하여 Wave 윈도우의 다음 Transition 을 찾을 수 있습니다.

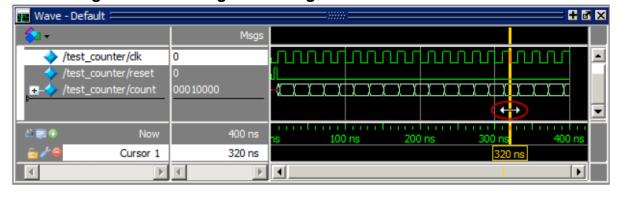

# Working with a Single Cursor

- 1. 클릭과 드래그를 통해 Cursor 이동하기

- A. Wave Window 의 toolbar 에서 Select Mode icon 을 클릭합니다.

ħ

B. Wave Window 의 파형이 그려지는 부분 아무 곳이나 클릭합니다.

클릭한 위치에 Cursor 가 나타납니다.

Figure 7-3. Working with a Single Cursor in the Wave Window

C. Cursor 드래그 하면서 Value 확인하기

Cursor 가 움직이면 Value 창에서 값이 변경되는 것을 볼 수 있습니다.

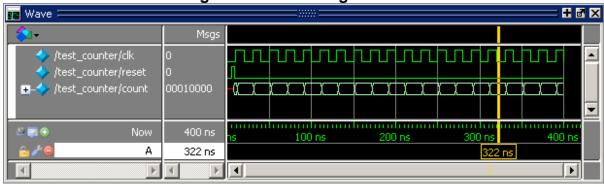

- 2. Cursor 의 이름 바꾸기

- A. Wave 윈도우의 Cursor 창에서 "Cursor 1" 마우스 오른쪽 버튼을 클릭합니다.

- B. Text 를 delete 키를 이용하여 삭제하고 A 를 입력합니다.

Cursor 의 이름이 A 로 변경된 것을 확인 할 수 있습니다.

Figure 7-4. Renaming a Cursor

- 3. Cursor 점프 이동 시키기

- A. Pathname 창에서 counter 를 클릭합니다.

- B. Wave 윈도우의 메뉴 중에서 아래의 아이콘을 클릭합니다.

선택한 Signal 의 next transition 으로 Cursor 가 점프하여 이동합니다.

- C. Wave 윈도우의 메뉴 중에서 아래의 아이콘을 클릭합니다. 이전의 transition 으로 Cursor 가 점프하여 이동합니다.

### **Working with Multiple Cursors**

- 1. Cursor 추가하기

- A. Cursor 를 추가하기 위해 아이콘을 클릭합니다. 崖

- B. 마우스 오른쪽 버튼을 이용하여 새로 추가된 Cursor 의 이름을 B 로 수정합니다.

- C. Cursor B 를 이동하면 자동적으로 A 와 거리가 측정됩니다.

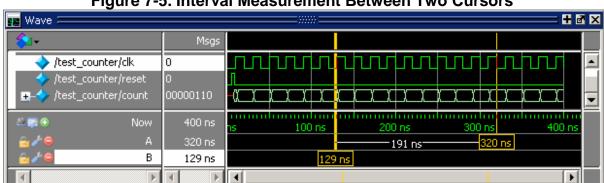

Figure 7-5. Interval Measurement Between Two Cursors

#### 2. Cursor B 고정하기

- A. Cursor B 를 56ns 근처로 이동시킵니다.

- B. 마우스 오른쪽 버튼을 클릭하여 나온 Pop up 메뉴에서 Lock B 를 클릭합니다.

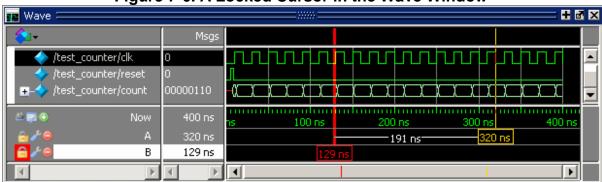

- 아래의 그림처럼 Cursor 가 빨간색으로 변경되며 움직여지지 않습니다.

Figure 7-6. A Locked Cursor in the Wave Window

#### 3. Cursor B 삭제하기

A. Cursor B 에서 마우스 오른쪽 버튼을 클릭하여 Delete B 를 선택합니다.

### Saving and Reusing the Window Format

유저 분이 Wave 윈도우를 닫아버리시면 지금까지 Wave 윈도우에서 했던 작업 (Signal 추가, Cursor 세팅) 같은 작업을 Wave 윈도우를 열 때 마다 다시 작업을 해야 합니다. 그러나, Save format command 를 이용하여 do file 로 format 을 저장하면 이러한 불편 없이 해당 format 을 이용하는 것이 가능합니다.

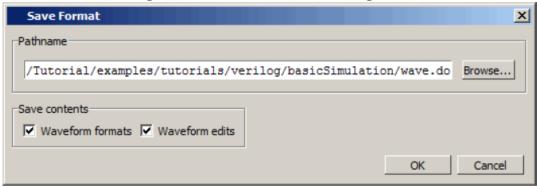

#### 1. Format file 저장하기

A. Wave 윈도우에서 File>Save format 을 선택합니다.

- B. 파일 이름을 Wave.do 파일로 수정하여 저장합니다.

- C. Wave 윈도우를 종료합니다.

#### 2. Format 파일 불러오기

- A. View>Wave 를 선택합니다.

- B. Wave 윈도우를 Undock 한 후에 Wave 윈도우에서 File>Load 를 선택합니다.

- C. 위에서 저장했던 wave.do 파일을 불러옵니다.

- D. 저장했을 당시의 Signal 들이 자동으로 추가됩니다.

- E. Wave 윈도우를 종료합니다.

- F. Simulate>End Simulation 을 선택하여 현재 진행중인 Simulation 을 종료합니다.

# Chapter 8 Creating Stimulus With Waveform Editor

Wave 윈도우에서 waveform Editor 를 이용하여 Simulation Stimulus 를 만들어서 Simulation 을 진행할 수 있습니다. 원하는 Simulation time 만큼 Stimulus 를 만들어서 Simulation 을 진행하고 해당 Stimulus 를 저장하여 추후에 사용 할 수도 있습니다.

이번 챕터에서는 이전에 사용했던 간단한 8 bit counter 응 이용하여 Simulation 을 진행할 것입니다. 예제 파일의 위치는 다음과 같습니다.

**Verilog** – <install\_dir>/examples/tutorials/verilog/basicSimulation

**VHDL** – <install\_dir>/examples/tutorials/vhdl/basicSimulation

이번 챕터에서 진행되는 Waveform Editor 는 유저 매뉴얼의 Generating Stimulus with Waveform Editor 나 Wave Window 를 보시면 좀 더 자세히 알 수 있습니다.

# **Compile and Load the Design**

1. 새로운 디렉토리를 만들고 tutorial file 복사하기

이번 챕터를 진행하기 위한 directory 를 만듭니다.

그리고 tutorial file 들을 새로 만든 디렉토리로 복사합니다.

- 2. ModelSim/Questa 를 실행되었으면 Change directory 를 이용하여 1번 과정의 directory 로 이동하기

- A. 바탕화면의 단축 아이콘 혹은 vsim command 를 이용하여 ModelSim/Questa 를 구 동합니다.

- B. File>change Directory 를 이용하여 1번 과정에서 만든 directory 를 지정합니다.

- 3. Working library 만들고 compile 하기

- A. vlib work 를 입력합니다.

- B. 해당 파일들을 compile 합니다.

Verilog

vlog counter.v

VHDL

vcom counter.vhd

- 4. Design Load 하기

- A. vsim -novopt counter 를 입력합니다.

- 5. Wave 윈도우 열기

- A. View>Wave 를 선택합니다.

# **Create Graphical Stimulus with a Wizard**

Waveform Editor 에는 Patten Wizard 가 포함되어 있습니다.

- 1. Patten Wizard 를 이용하여 Clock 만들기

- A. Object 윈도우에서 clk 를 선택하고 마우스 오른쪽 버튼을 클릭하여 Create Wave 를 선택합니다.

Figure 8-1. Initiating the Create Pattern Wizard from the Objects Window

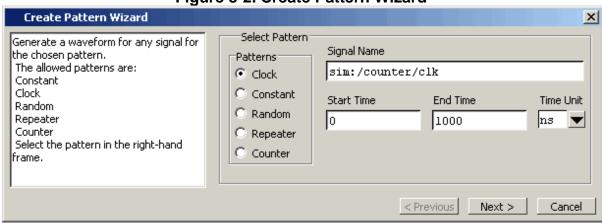

B. Patten Wizard 창이 열리면 Clock 를 선택하고 아래의 그림과 같이 설정합니다.

Figure 8-2. Create Pattern Wizard

C. 두 번째 창이 열리면 다시 한번 아래와 같이 설정합니다.

Figure 8-3. Specifying Clock Pattern Attributes

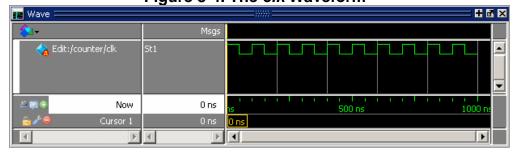

위와 같이 설정을 하고 Finish 버튼을 클릭하면 아래와 같이 Clock Patten 이 만들어 집니다.

Figure 8-4. The clk Waveform

- 2. Wizard 를 이용하여 또 다른 Signal 만들기

- A. Object 윈도우에서 reset 를 선택하고 마우스 오른쪽 버튼을 클릭하고 Create Wave

를 선택합니다.

- B. Patten 타입을 Constant 를 선택하시고 Next 를 선택합니다.

- C. Value 에 0 를 입력하고 Finish 를 클릭합니다. 두 번째로 만들어진 파형이 Wave 윈도우에 보여집니다.

Figure 8-5. The reset Waveform

#### **Edit Waveforms in the Wave Window**

Waveform Editor 는 Patten Wizard 뿐만 아니라 editing 할 수 있는 여러 Command 를 제공하고 있습니다. (invert, mirror, stretch edge, cut, etc.)

- 1. reset 에 Pulse 삽입하기

- A. Edit Mode 를 활성화하기 위해 아래의 아이콘을 클릭합니다. 🟥

- B. Pathnames 에서 reset 를 선택합니다.

혹은, Wave 윈도우에서 reset 를 선택하고 마우스 오른쪽을 클릭하여 Wave>Wave Editor>Insert Pulse 를 클릭합니다.

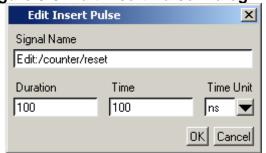

D. Insert Pulse 를 선택하고 아래의 창과 같이 입력합니다.

Figure 8-6. Edit Insert Pulse Dialog Box

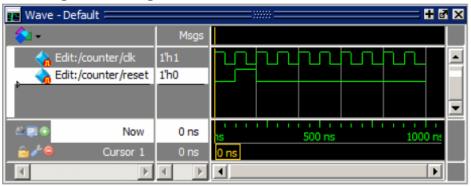

OK 를 클릭하면 reset 의 100ns 에서 200ns 사이에 High 신호가 나타납니다.

Figure 8-7. Signal reset with an Inserted Pulse

- 2. clk 의 edge 늘리기

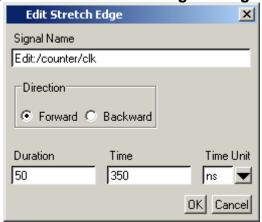

- A. Wave 윈도우에서 clk 를 클릭하고 마우스 오른쪽 버튼을 클릭하여 Wave Editor>Stretch Edge 를 클릭합니다.

- B. 창이 열리면 Duration 에 50, Time 에 350 를 입력하고 OK 를 클릭합니다.

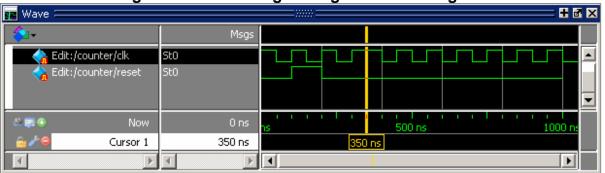

Figure 8-8. Edit Stretch Edge Dialog Box

OK 를 클릭하여 300~400ns 사이에 high 가 유지되는 파형으로 변경됩니다.

Figure 8-9. Stretching an Edge on the clk Signal

3. Edge 지우기

- A. Cursor 를 400ns 근처에 놓고 clk 를 클릭합니다.

- B. Delete Edge 아이콘을 클릭합니다.

아이콘을 클릭하면 창이 열립니다.

창이 열리면 Time 에는 400 ns 를 입력하고 OK 버튼을 클릭합니다.

Wave - Default

Msgs

Edit:/counter/clk

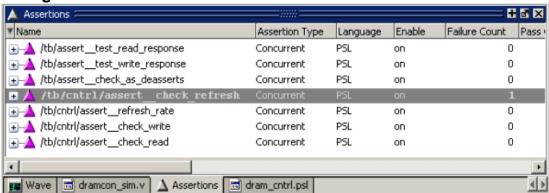

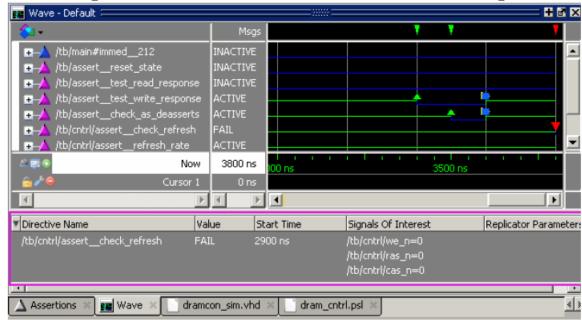

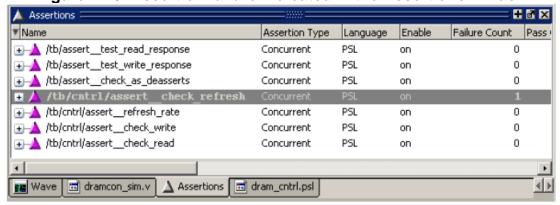

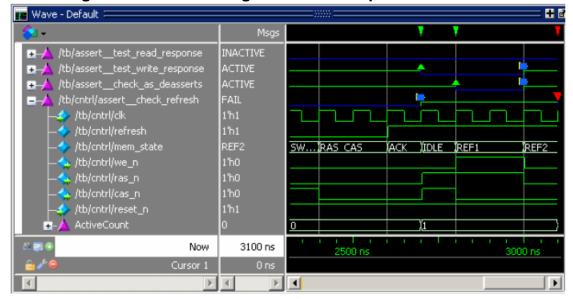

Now

Ons

Cursor 1

400 ns

Figure 8-10. Deleting an Edge on the clk Signal

clk 는 400~500ns 사이에 있던 edge 가 사라지고 위와 같이 파형이 나타납니다.

- 4. Undo 와 Redo 를 이용하여 edit 하기

- A. Undo 아이콘을 클릭합니다. Undo 아이콘을 클릭하여 Undo Count 를 물어보는 창이 나타납니다. 1 를 입력하고 OK 를 클릭하면 Delete Edge 하기전의 파형으로 돌아갑니다.

- B. clk 을 다시 선택하고 Redo 아이콘을 클릭합니다. Redo 아이콘을 클릭하면 마찬가지고 Redo Count 를 물어보는 창이 나타나고, 1 를 입력하면 Delete Edge 가 진행된 형태로 파형이 나타납니다.

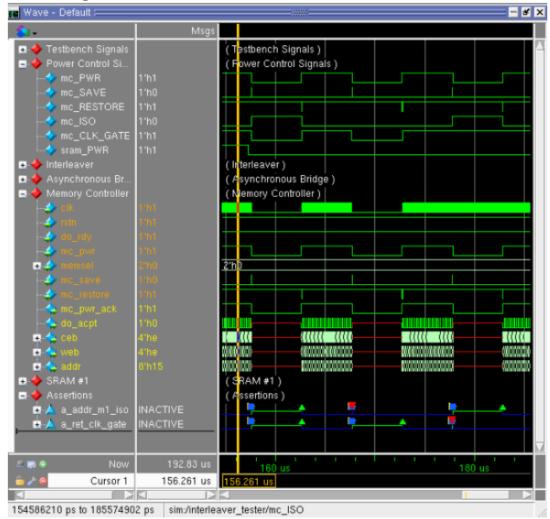

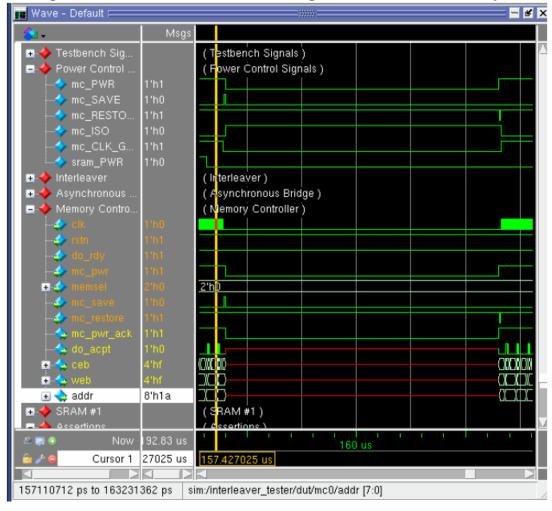

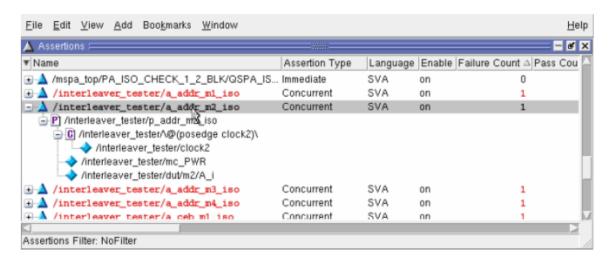

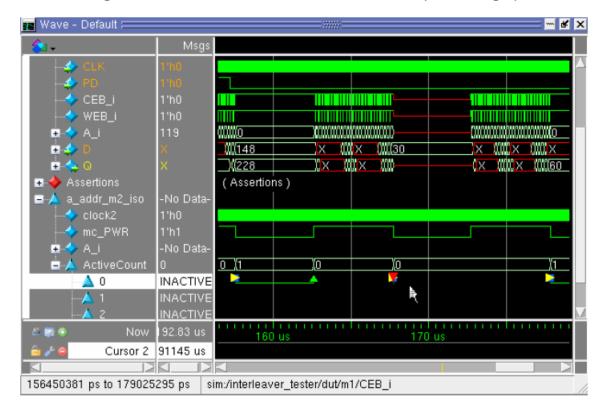

#### Save and Reuse the Wave Commands

ModelSim/Questa 에서 작업한 Waveform Stimulus 를 특정한 Format 의 파일로 저장할 수 있습니다. 또한 Load 를 해서 반복적으로 사용할 수도 있습니다.

- 1. Format File 저장하기

- A. Wave command 를 저장하기 위해 File>Save Format 를 선택합니다.

Figure 8-11. Save Format Dialog Box

기본적으로 File 이름은 wave.do 로 저장됩니다.

- B. Yes 를 클릭합니다.

- C. File name 필드에 waveedit.do 를 입력하고 Save 를 클릭합니다. 이제 Waveform 은 waveedit.do 파일로 저장이 됩니다.

- 2. Simulation 종료하고 다시 Design 로드하기

- A. Simulate>End Simulation 을 선택하여 Simulation 을 종료합니다.

- B. 다시 Design 을 로드하기 위해 아래의 Command 를 입력합니다. vsim -novopt counter

- 3. Format File 열기

- A. View>Wave 를 클릭하여 Wave 윈도우를 엽니다.

- B. File>Load 를 선택하고 앞에서 저장했던 waveedit.do 파일을 클릭합니다.

이제 앞서서 저장했던 Wave 파형이 Wave 윈도우에 나타난 것을 확인 할 수 있습니다.

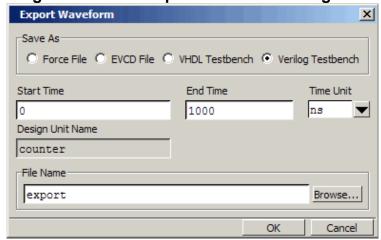

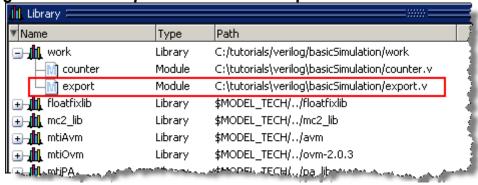

### **Exporting the Created Waveforms**

앞에서는 do 파일 format 을 저장하는 방법을 살펴보았으나 여기서는 4개의 파일 Format 중에 원하는 형태로 저장하는 방법을 살펴보겠습니다.

- 1. Created Waveform 을 HDL Test bench 파일 Format 으로 저장하기

- A. File>Export>Waveform 을 선택합니다.

- B. Save as 부분을 VHDL Test bench 혹은 Verilog Test bench 를 선택합니다.

- C. End Time 부분은 1000 을 입력합니다.

- D. File Name 에는 export 를 입력하고 OK 버튼을 클릭합니다.

Figure 8-12. The Export Waveform Dialog Box

ModelSim/Questa 는 현재 디렉토리에 export.vhd 혹은 export.v 라는 이름으로 test bench 파일을 저장합니다.

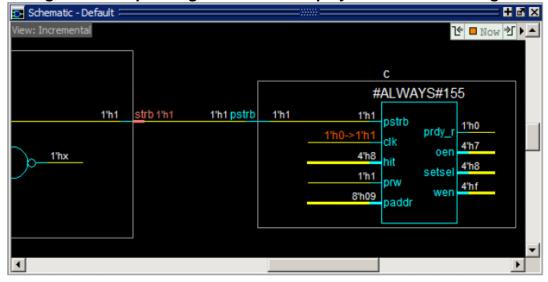

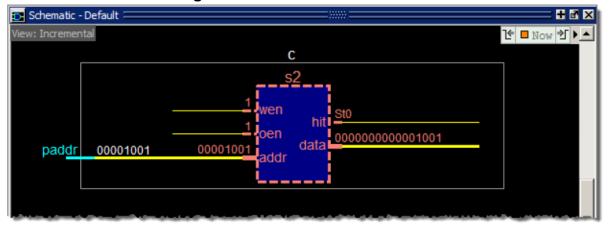

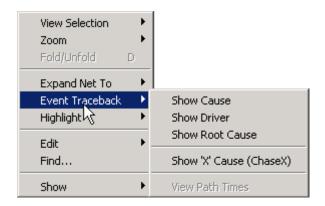

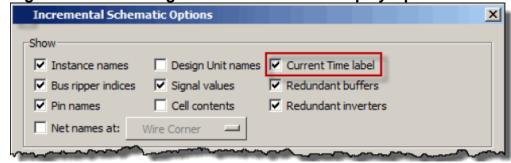

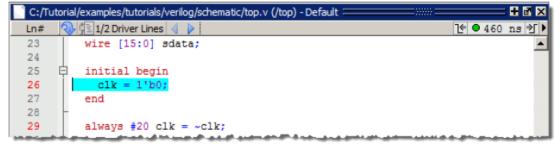

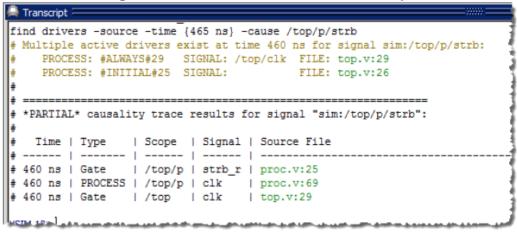

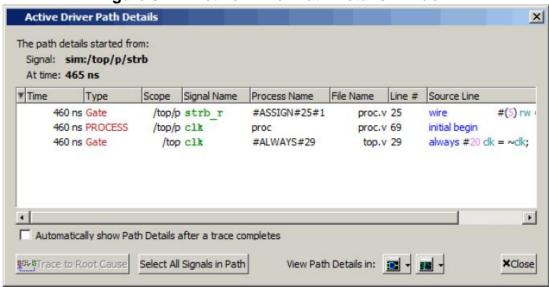

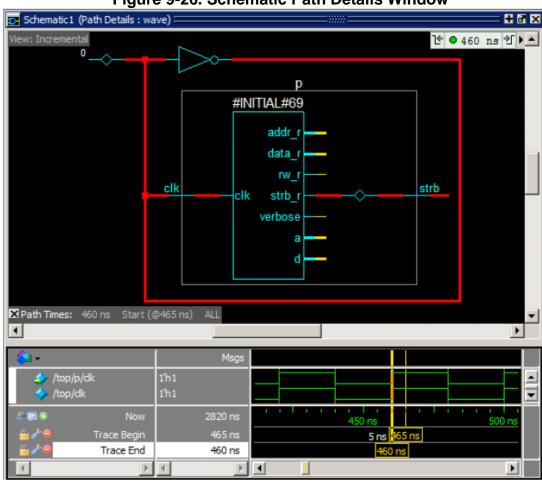

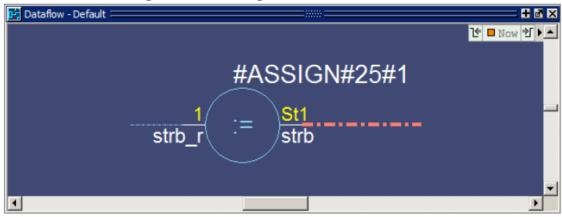

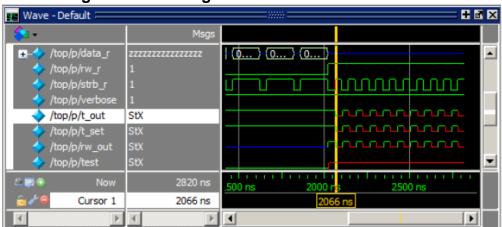

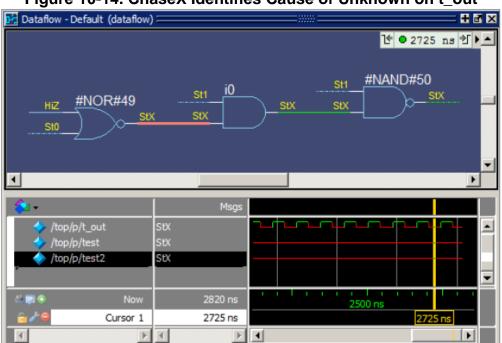

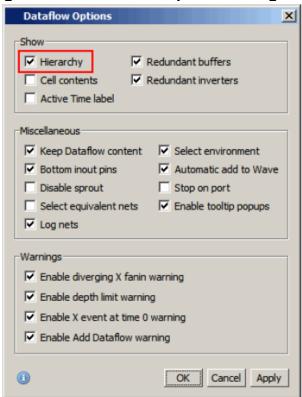

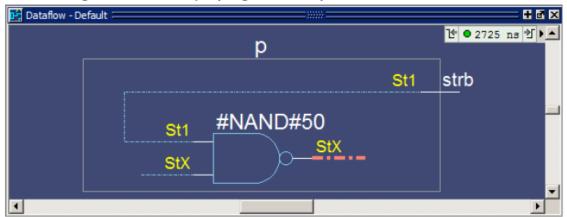

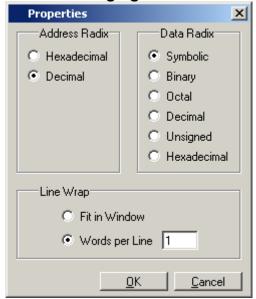

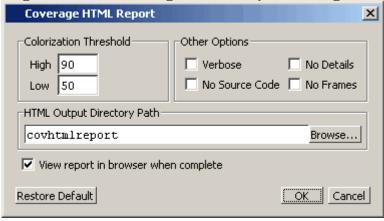

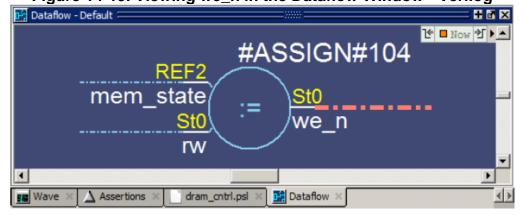

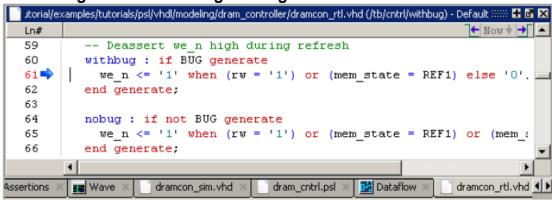

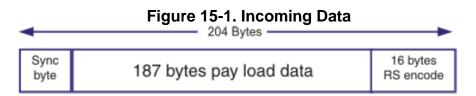

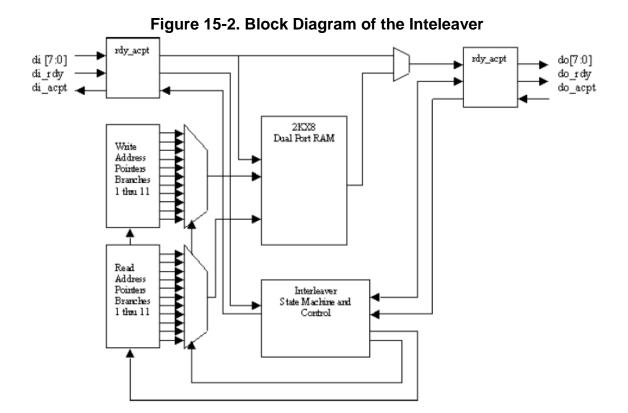

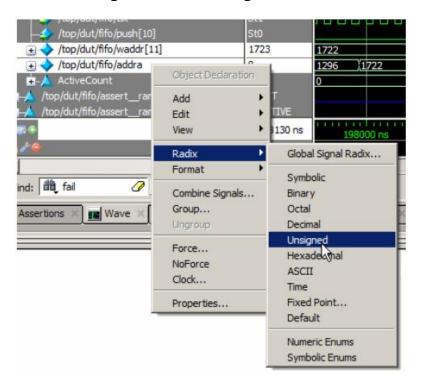

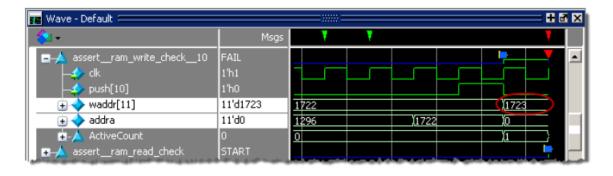

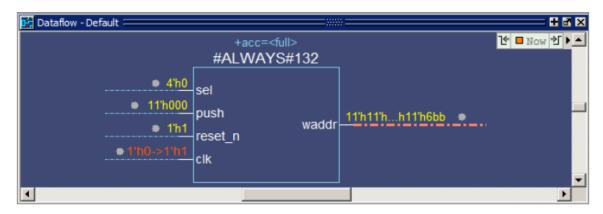

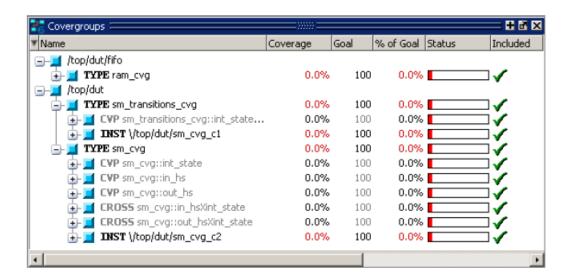

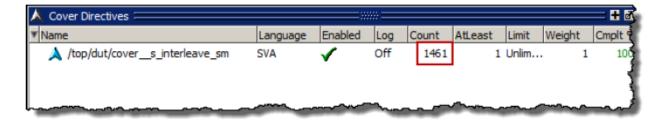

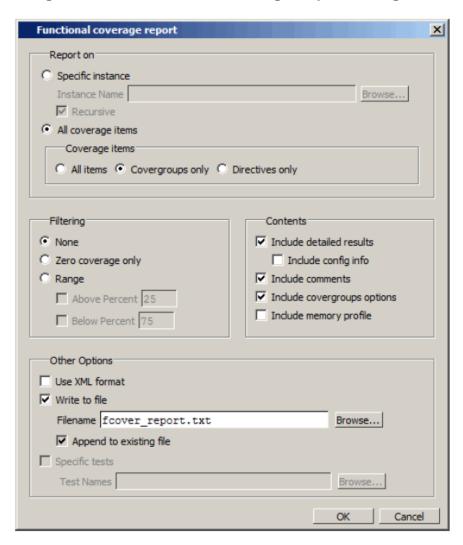

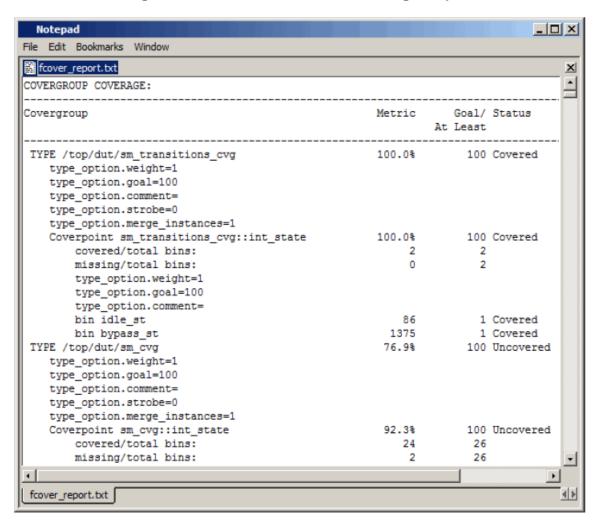

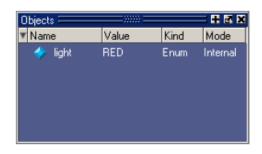

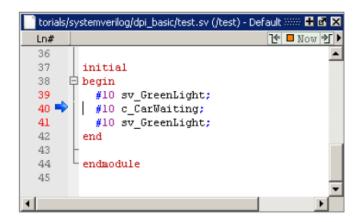

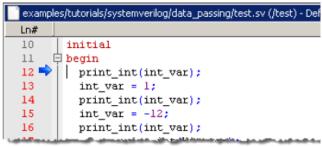

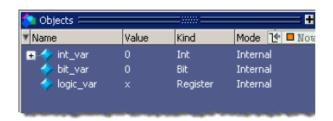

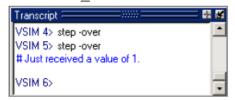

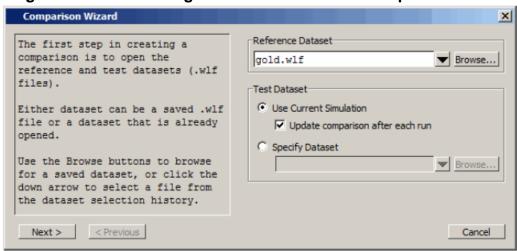

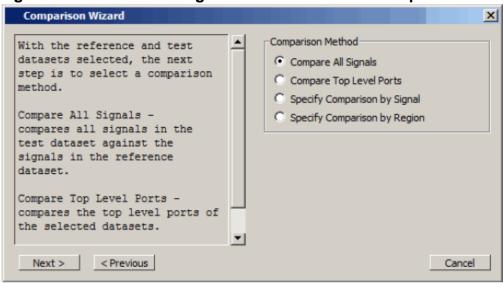

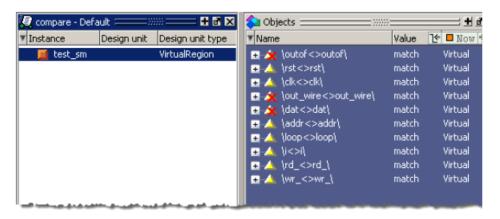

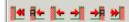

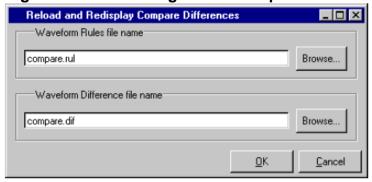

- 2. VCD Format 을 저장하기