# MEMS + 5.0 for MEMS Device Design

**Explore Concepts**

**Optimize Designs**

**Predict Yield**

## The Challenge

MEMS development takes too long...

- Conventional FEA (finite element analysis) is time consuming, even for assessing basic behavior...

- Full multi-physics coupling is approximated or ignored (this can make or break devices)

- Transient simulations are often infeasible because they take too long

- Yield studies are not performed

- Numerous, time consuming in-fab learning cycles are used in place of simulation

- Market windows are missed!

## The Solution

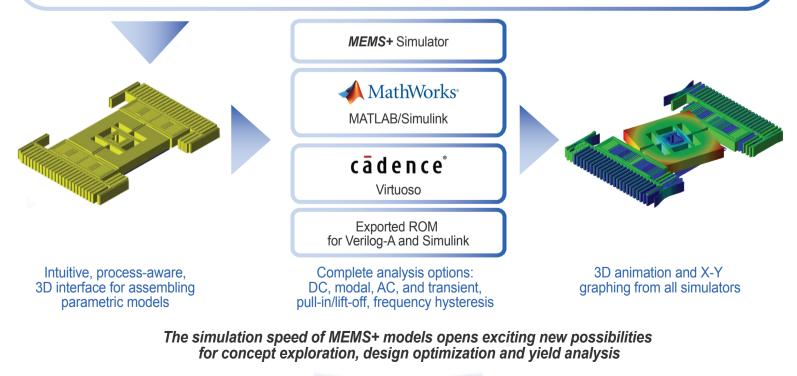

#### Reduce development time using MEMS+ models

- Assemble models from a library of MEMS-specific, highorder, parametric finite elements

- MEMS+ models are compact (10s to 1,000s unknowns) and simulate really fast ( > 100X faster than FEA)

- The same model runs in multiple simulators: *MEMS+*, MATLAB, Simulink, and Cadence Virtuoso

- Fully coupled multi physics: mechanics, electrostatics, piezo, thermal, gas damping, packaging and more...

- Non-linear effects included: mechanical and electrostatic; pull-in, lift-off, spring softening; quadrature, frequency hysteresis, ...

### **MEMS+** Component Library: MEMS-specific, 3D, high-order, parametric finite elements

Everything needed to assemble multi-physics models of complex, real-world sensor and actuator designs

# MEMS+® 5.0 for MEMS+IC Co-Design

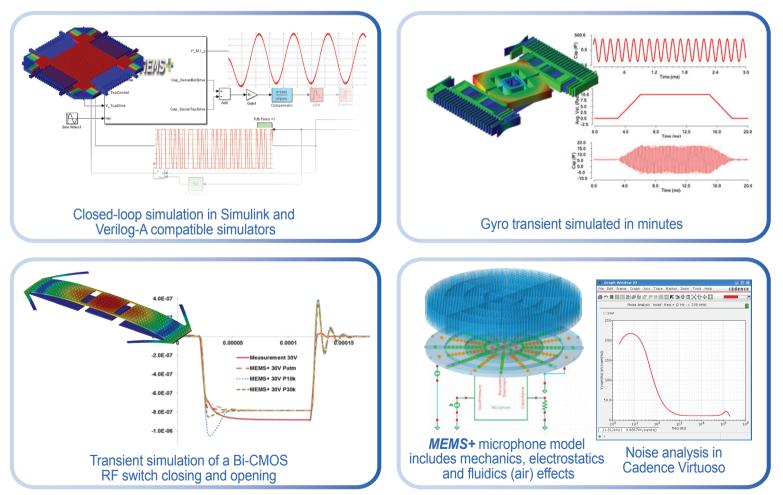

Closed Loop

**Corner Cases**

#### **Noise Analysis**

## The Challenge

Months are wasted on hand-crafting different MEMS device models for system and IC designers.

- Different models for different users...

- System designers use MATLAB/Simulink

- IC designers use SPICE or Verilog-A

- MEMS designers use FEA

- Hand-crafted MEMS models for Simulink, SPICE, or Verilog-A are common practice. These are...

- Inaccurate due to over-simplification: Degrees of freedom and non-linear effects are neglected

- Not parametric with respect to design or environment variables

- Prone to human error and rapidly go out of sync between design groups

## The Solution

Use *MEMS*+ to generate one model for everyone. Save months and avoid design errors.

- A single *MEMS*+ model is the source for all formats: MATLAB, Simulink and Verilog-A

- Redundant modeling effort is eliminated

- Generated ROMs are tunable for accuracy versus simulation speed

- Selectively include mechanical degrees of freedom and non-linear effects

- Selectively expose design and environment variables in system and circuit symbols

- A source of human error is removed and it's easier for design teams to stay in sync

MEMS+ takes MEMS+IC co-design to a whole new level!