# Model Diagnoser<sup>TM</sup>

Ultimate Verification, Quality Assurance and Interactive Debugging for .Lib Model of Cell Library

# Agenda

#### Introduction

- Model Diagnoser Flow

- Setup/hold time diagnosis for function/noise violations

- Repairing library model from function/noise violations

- Inaccuracy diagnosis by library model comparison

- Function verification between views of library model

- CCS consistency check of library model

- Interactive Debugging

- The Conclusion

Legend Design Technology

## **Legend's Products**

#### IP Library Verification/Characterization Products

- Model Diagnoser<sup>TM</sup>: *Cell Library QA*, *Diagnosis and Debugging*

- Charflo-Cell!<sup>TM</sup>: Automatic Cell/IO Library Characterization

- Charflo-Memory!<sup>TM</sup>: *Automatic Memory Characterization*

- Circuit Simulation Products

- MSIM<sup>®</sup>: Accurate-Spice Simulator for Analog/RF/Mixed-Signal IC and IP, LCD, and PCB/IBIS/Package

- PCB Design Manager: Integrated Schematic & Simulation Environment with Test Bench Automation

- Turbo-MSIM<sup>TM</sup>: *Fast-Spice Simulator*

## The Problems Standard /IO Cell Library Modeling

The .Lib model of standard / IO cell library may be

- Incorrectly modeled or characterized

- Inappropriately applied at new PVTs

Need QA process to assure the .Lib timing model

- No functional failures shall be resulted

- Noise on output pins shall be within the margin

- Timing, power and noise models are valid in accuracy

- No over-excessive timings degrading speed seriously

• Need repairing .Lib model to meet the QA criteria

## **The Solutions** Model Diagnoser<sup>TM</sup> Functions

Setup/hold time diagnosis for function/noise violations

Repairing library model from function/noise violations

Inaccuracy diagnosis by library model comparison

Function verification between views of library model

CCS consistency check of library model

Interactive Debugging

## **The Necessities**

#### Model Diagnoser on top of Characterization

- Use ultimate validation, different from characterization

- Verify setup/hold time by directly plugging into final simulation, instead of bi-section with error tolerances

#### Check internal nodes, not covered by characterization

- Examine glitches and noise strengths on internal nodes, instead of 'output pins only' by simulator's bi-section

- Trust but verify possible errors in characterization from

- Characterization tools

- Simulation tools

- Human mistakes and manual settings

Legend Design Technology

## TSMC's Selection Model Diagnoser™

TSMC Selects Legend's Model Diagnoser for Standard Cell Library Quality Assurance

http://www.legenddesign.com/BW/060909.shtml

"Legend's Model Diagnoser can help locate the functional issues in the .lib models of TSMC 90nm and 65nm standard cell libraries. We are satisfied with the tool results, and continue to work with Legend to ensure our library quality for advanced nanometer technologies,"

said Tom Quan, deputy director of design service marketing at TSMC.

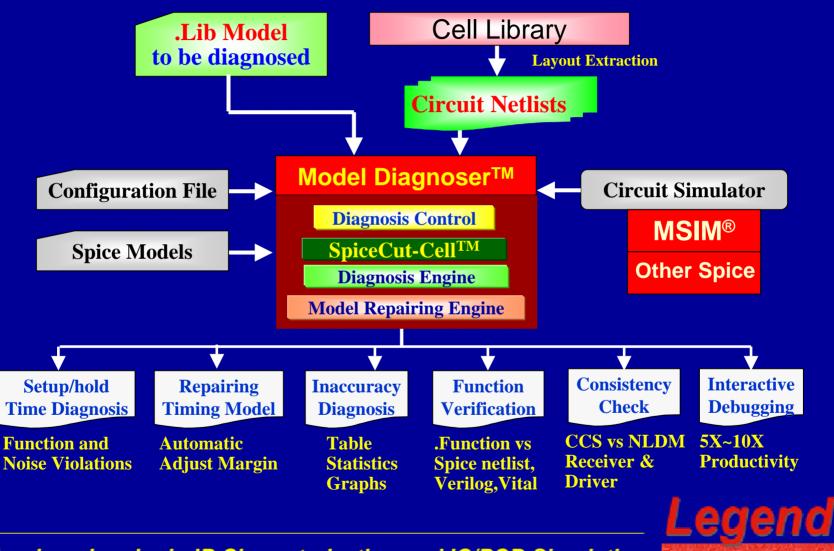

## Model Diagnoser<sup>™</sup> Flow

Technology Leader in IP Characterization and IC/PCB Simulation

Design Technology

### Setup/Hold Time Diagnosis Function & Noise Check on Latch/Flip-flop

- Analyze the circuit of each cell by SpiceCut tool, and locate high-risk spots inside the cell.

- Build all possible state patterns based on functions and conditions in .Lib, and set up corresponding stimulus.

- Simulate the cell by applying setup/hold time, and min. pulse width from .Lib, with the stimulus built.

- Verify the simulation results for locating functional failures and noise violations (e.g. glitch)

- Locate over-excessive timings (e.g. min. clock width) to prevent from serious performance degrading

### **SpiceCut-Cell Functions** Circuit Analysis & Pattern Recognition

- Build circuit database of nodes and MOSFETs, and extract subcircuit configurations.

- Locate the high-risk nodes inside the cells to monitor for ensuring the modeling quality.

- Identify the measurable nodes inside the cells before tri-state output for complex I/O cell characterization.

- Perform pattern recognition over the circuits of standard cells, complex cells and customized cells.

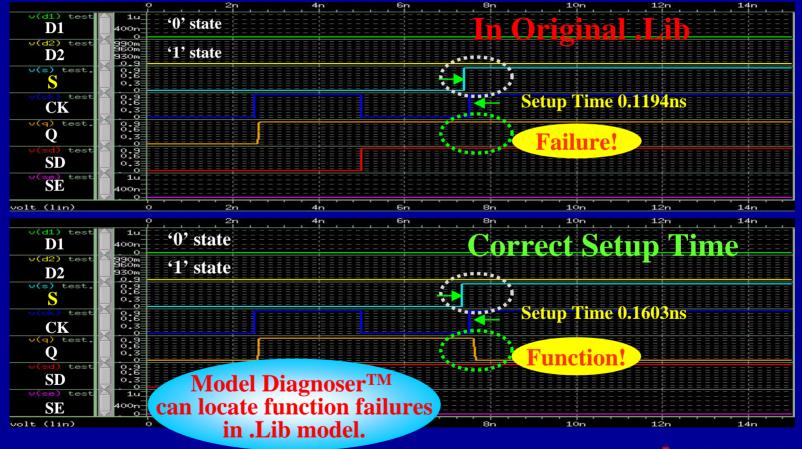

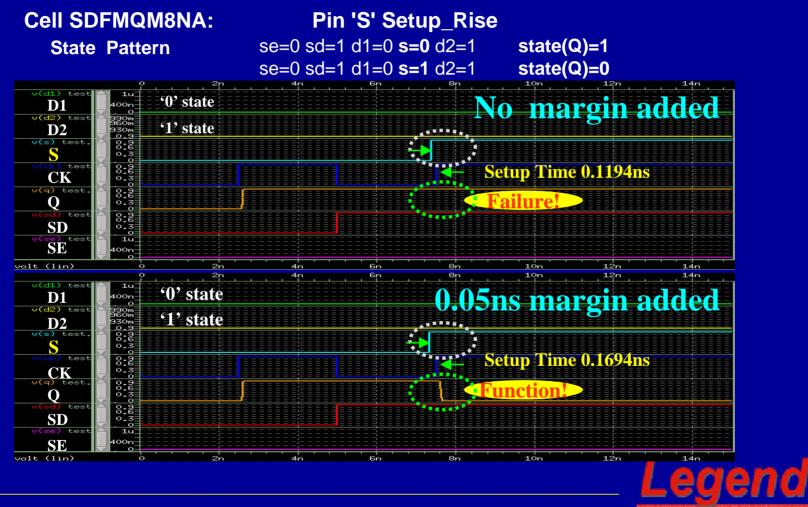

#### **'Function' Violation** Due to Insufficient Setup Time

Technology Leader in IP Characterization and IC/PCB Simulation

Legend Design Technology

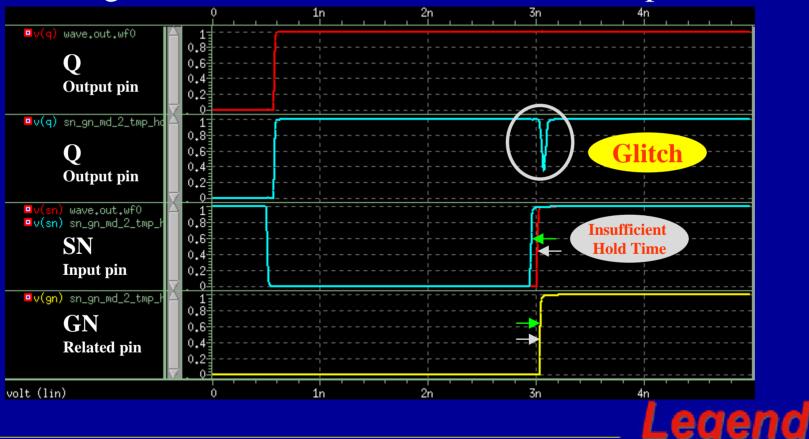

### Output-Pin 'Glitch' Violation Due to Insufficient Hold Time

◆ The glitch is of 66% Vdd with the width 37ps.

Technology Leader in IP Characterization and IC/PCB Simulation

Design Technology

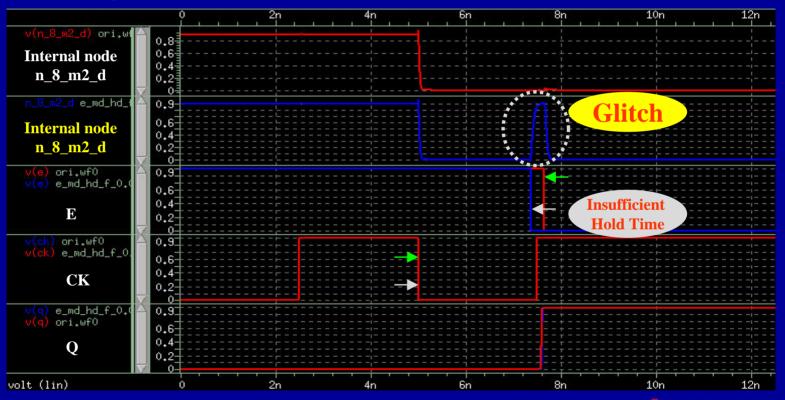

#### Internal 'Glitch' Violation Due to Insufficient Hold Time

#### ◆ The glitch is of 96% Vdd with the width 0.303ns.

Technology Leader in IP Characterization and IC/PCB Simulation

Legene Design Technology

### Run-Statistics Examples Function & Noise Check on Latch/Flip-flop

#### Diagnosing one cell library normally takes 2~4 hours

| Cell Library             | Number<br>of Latch &<br>FlipFlop Cells | Add N<br>0.05ns/ 0. | Violation-Free<br>Margin to add |               |

|--------------------------|----------------------------------------|---------------------|---------------------------------|---------------|

|                          |                                        | Function Violation  | Glitch* Violation               |               |

| <b>40nm</b> (857 cells)  | 158                                    | 46/4/2              | 0/ 0/ 0                         | <b>0.25ns</b> |

| <b>55nm</b> (1084 cells) | 294                                    | 2/ 0/ 0             | 15/ 5/ 1                        | <b>0.22ns</b> |

| <b>65nm</b> (814 cells)  | 228                                    | 28/ 0/ 0            | 13/ 0/ 0                        | <b>0.1ns</b>  |

| <b>90nm</b> (837 cells)  | 251                                    | 76/71/10            | 130/ 126/ 1                     | <b>0.3ns</b>  |

|                           |     | Add M<br>0.5ns/ 1.0 | Violation-Free<br>Margin to add |              |

|---------------------------|-----|---------------------|---------------------------------|--------------|

| <b>0.18um</b> (594 cells) | 145 | 51/2/1              | 0/ 0/ 0                         | <b>2.4ns</b> |

| <b>0.35um</b> (588 cells) | 139 | 97/ 45/ 20          | 0/ 0/ 0                         | <b>1.7ns</b> |

\* Report 'Glitch Violation' only when (1) glitch\_height > 40% of Vdd (2) glitch\_width > 20ps (3) glitch\_height\_in\_V \* glitch\_width\_in\_ps > 20 V-ps

### **Repairing Library Model** To Prevent from Function/Noise Violations

- For setup/hold time & min pulse width in .Lib model, the margin shall be automatically adjusted to ensure

- No functional violations

- No glitch violations on internal nodes and output pins

- No over-excessive timings degrading performance seriously

- Margin increment can be by values or by percent

- Margin adjustment for tabular setup/hold time can be determined by the worst corner, by four extreme corners and the central, or by all entries of that table.

#### **Repair .Lib Model** Add Margin 0.05ns to Setup Time

Technology Leader in IP Characterization and IC/PCB Simulation

Design Technology

### Correct 'Excessive Spike' in .Lib To Prevent from Serious Speed Degrading

- 'Excessive Spike' entry in the table of setup/hold time & min pulse width in .Lib model could cause

- Difficult to keep monotonic table as required by PrimeTime

- Large performance sacrifice (e.g. due to min clock width)

- Simulate the cell by applying the 'reduced' setup/hold time & min pulse width, i.e. adding 'negative' margin.

- At the various negative margins, verify the simulation results for locating functional 'success' without noise violations. Then, report the necessary corrections.

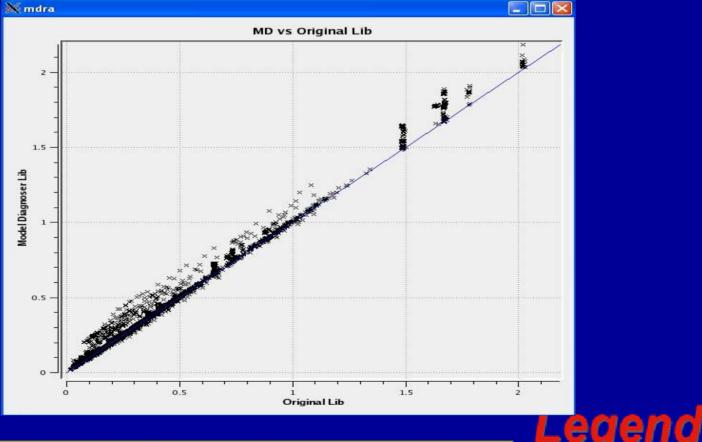

## **Inaccuracy Diagnosis** By Library Model Comparison

- Diagnose the inaccuracy of target library by comparing its .Lib model with the re-characterized one by using Model Diagnoser.

- The difference between the tables of parameters will be represented by

- Table report

- Statistical report

- 2D Graphical report

- 3D Graphical report

Legend Design Technology

### Inaccuracy Report Sorted Timing-Arc and Statistical Report

#### Statistical report can be used for measuring overall quality of target library, at cell or parameter level.

| Cell    | Template        | Pin(s)                      | Parameter     | Diff   | Diff % | New Value   | Orig. Value         | When       | Index1   | In       | dex2        |            |

|---------|-----------------|-----------------------------|---------------|--------|--------|-------------|---------------------|------------|----------|----------|-------------|------------|

| mffnrb1 | falLtransition  | Q -> cp                     | delay         | 0.0156 | 51.93  | 0.04558     | 0.03                |            | 2.1 ns   | 0 pf     |             |            |

| mffnrb1 | falLtransition  | QN -> cp                    | delay         | 0.0223 | 45.48  | 0.0712875   | 0.049               |            | 1.05 ns  | 0 pf     |             |            |

| mffnrb1 | fall_transition | Q -> cp                     | delay         | 0.0130 | 43.43  | 0.0430275   | 0.03                |            | 1.05 ns  | 0 pf     |             |            |

| mffnrb1 | falLtransition  | QN -> cp                    | delay         | 0.0201 | 42.81  | 0.06712     | 0.047               |            | 0.245 ns | 0 pf     |             |            |

| mffnrb1 | falLtransition  | Q -> cp                     | delay         | 0.0105 | 34.89  | 0.0404675   | 0.03                |            | 0.245 ns | 0 pf     |             | \$50       |

| mffnrb1 | falLtransition  | Q -> cp                     | delay         | 0.0102 | 33.91  | 0.0401725   | 0.03                |            | 0.07 ns  | 0 pf     |             | 100        |

| mffnrb1 | rise_transition | Q → cp                      | delay         | 0.0102 | 30.98  | 0.0432225   | 0.033               |            | 0.01 ns  | 0 pf     |             |            |

| mffnrb1 | falLtransition  | Q → cp                      | delay         | 0.0211 | 30.97  | 0.08906     | 0.068               |            | 0.245 ns | 0.007 pf |             |            |

| mffnrb1 | rise_transition | QN -> cp                    | delay         | 0.0127 | 30.90  | 0.0536675   | 0.041               |            | 1.05 ns  | 0 pf     |             |            |

| mffnrb1 | rise_transition | Q -> cp                     | delay         | 0.0098 | 29.74  | 0.042815    | 0.033               |            | 0.245 ns | 0 pf     |             |            |

| mffnrb1 | rise_transition | Q -> cp                     | delay         | 0.0097 | 29.32  | 0.042675    | 0.033               |            | 0.035 ns | 0 pf     |             |            |

| mffnrb1 | falLtransition  | QN -> cp                    | delay         | 0.0269 | 26.66  | 0.127922    | 0.101               |            | 2.1 ns   | 0.007 pf |             |            |

| mffnrb1 | rise_transition | Q -> cp                     | delay         | 0.0087 | 26.39  | 0.0417075   | 0.033               |            | 0.07 ns  | 0 pf     |             |            |

| mffnrb1 | falLtransition  | QN -> cp                    | delay         | 0.0130 | 24.94  | 0.06497     | 0.052               |            | 2.1 ns   | 0 pf     |             | -          |

| mffnrb1 | rise_transition | QN -> cp                    | delay         | 0.0102 | 24.94  | 0.051225    | 0.041               |            | 0.245 ns | 0 pf     |             | -          |

| -       | tries .         | Avg Diff                    | Avg Diff %    |        | Sigma  | Max Diff    | Max Dr              | ff as      | Min D    |          | Min Diff 9  |            |

| Ent     | ALCONT A        | Roca <del>t</del> o Accesso | 100 - 000 000 |        |        | Constraints | and an and a second | No.Phylane | 100000   |          | Will Dill 9 | Sector and |

| •       | 18              | 0.0150                      | 0 31.9        | 765    | 0.0056 | C           | 0.03                | 51.93      |          | 0.0087   |             | 22.1       |

#### Technology Leader in IP Characterization and IC/PCB Simulation

Design Technology

Lea

### **2D/3D Graphic Report** Based on Statistics of Cell & Parameter

#### 2D Graphic Report

Technology Leader in IP Characterization and IC/PCB Simulation

Design Technology

## **Function Verification** Between Views of Library Models

Check the consistency between function description (i.e. .FUNCTION statements) in .Lib and

- Spice netlist at transistor level

- Verilog descriptions

- \*Vital descriptions

Report the difference of their derived state patterns

\* Vital verification will be released in Q3, 2010

Legend Design Technology

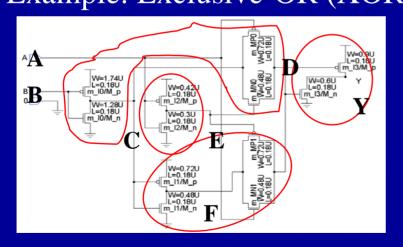

#### **Extract Cell Functions** Directly from Spice Circuit Netlist

Standard cells are normally by static designs. Their subcircuits and functions are quite straightforward.

SpiceCut-Cell can partition/recognize those subcircuit patterns, and extract their corresponding functions.

Example: Exclusive-OR (XOR) Cell

$$C = -B; \quad F = -C = B; \quad E = -A;$$

$$D = C * E + F * (-E)$$

$$= (-B) * (-A) + B * A$$

$$Y = (-A) * (-B) + A * B$$

$$Y = A ^{B}$$

### Verify Functions in .Lib Against Functions Extracted from Circuits

- Extract the logic functions directly from cell circuit netlist by SpiceCut-Cell

Validate the FUNCTION statement of each

- timing arc in the existed .Lib model, by comparing with those circuit-extracted ones.

- Confirm the specifications of related\_pin, timing\_sense, when, and sdf\_cond etc. in the existed .Lib model.

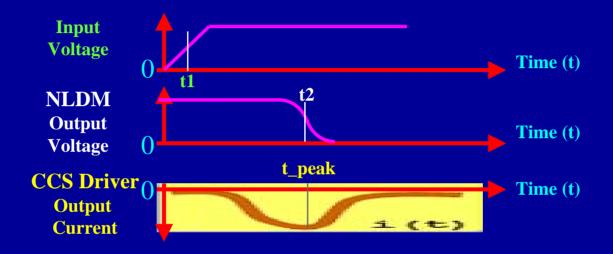

## **CCS Model Check**

CCS Receiver Model Consistency Check Compare CCS' C1 and C2 with NLDM input capacitance

CCS Driver Model Consistency Check Compare CCS waveform's peak time with NLDM delay

CCS Driver Model Integration Check

- $I = C * dV / dt \implies \int I dt / C = V dd$

- Difference between  $\int I dt/C$  and Vdd need be < 5%

Leaend

**Design Technology**

### **CCS Driver Model** CCS vs NLDM Consistency Check

- NLDM\_delay = t2 t1

- CCS\_delay from driver model = t\_peak t1

- Consistency can be checked by comparing CCS\_delay with NLDM\_delay, and reporting the difference.

Ledend

Technology Leader in IP Characterization and IC/PCB Simulation Design Technology

## **Interactive Debugger**

Click the selected violation or timing-arc, and the windows of circuit stimulus/netlist and waveform viewer will automatically pop up.

• Users can Edit/Save, Simulate and View Waveforms.

| X /legend.us/data1/yw                                                                                                                                                                                                                                                                                                                                                                                    | vu/tower_cell_0114/choo | ose_0511 📕 🗖 🔀        | 躍 MVIEW v100329 (C) Copy            | rright 2010 Legend Design | n Technology, Inc.                                                   |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------|-------------------------------------|---------------------------|----------------------------------------------------------------------|--|

| Save As                                                                                                                                                                                                                                                                                                                                                                                                  | Run MSim                | Run MView             | <u>File View Panel Window H</u> elp |                           |                                                                      |  |

| <pre>* File:<br/>/legend.us/data1/ywu/tower_cell_0114/choose_0511_rserv1/characterix<br/>at ion/decfq1/q/cpn_dly_cel_r.hsp<br/>\$<br/>.global vdd gnd vss<br/>.opt nomsd<br/>.opt autostop post tstepoff<br/>.lib<br/>'/legend.us/data1/ywu/tower_cell_0114/choose_0511_rserv1/spice_mode<br/>1/ts1013dig.lib' tt_12b3<br/>.param vih=1.200<br/>.param vih=0.0<br/>.temp 25.000<br/>VVDD VDD 0 1.2</pre> |                         | cpn_dly_cel_r.a14.wf0 | Panel 1.<br>VQ)                     |                           |                                                                      |  |

| <pre>VVSS VSS 0 vil     stimulum section {    Piecewise linear way    VCPN CPN 0 PAL    ' 0n+0.5 tCycle' vil    ' 0n+0.5 tCycle' alwey    ' 0n+1.6 tCycle' alwey    ' 0n+1.5 tCycle' vil    ' 0n+1.5 tCycle' vil    ' 0n+1.5 tCycle' vil    Piecewise linear way    vormed a par </pre>                                                                                                                  | vil<br>vil              |                       |                                     | v(d)                      | 1.14<br>0.78<br>0.42<br>60<br>60<br>0<br>0<br>197n 394n 59n 7.87n 98 |  |

## Conclusion Model Diagnoser<sup>™</sup>

- Enable quality assurance of cell library .Lib models which are critical for SoC designs.

- Quickly locate the function, noise, timing and power violations in the cell library .Lib model at any PVT.

- Repair .Lib model of latch/flip-flop by automatically adjusting the margins for production yields.

- Easy to use with Interactive Debugger by GUI, and programmable configurations.

- Fully proven for production flow.

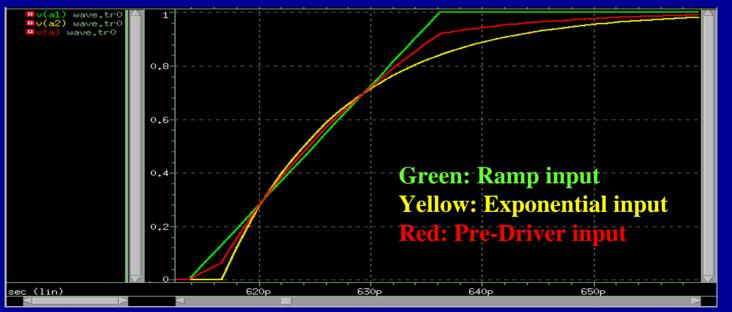

## **Pre-Driver Input Waveform** For 45nm Cell Characterization

Pre-driver method is analogous to taking the output of a PWL source and passing it through a low-pass filter.

Model Diagnoser supports both ramp and pre-driver input

#### Criteria for 'Glitch' Violation Noise Check on Latch/Flip-flop

Command Format for criteria of Glitch violation

*Glitch 0.6 50 30*

Report Glitch violation when

(glitch\_height > 60% of Vdd) AND

(glitch\_width > 50ps) AND

(glitch\_height\_in\_V \* glitch\_width\_in\_ps > 30 V-ps)

Default values for criteria of Glitch violation

Glitch 0.3 10 10

## Legend's Patents Model Diagnoser™

United States Patent 7231336 "Glitch and metastability checks using signal characteristics" • United States Patent 7131088 "Reliability based characterization using bisection" United States Patent 7203918 "Delay and signal integrity check and characterization" • United States Patent 6112022 "Method for simulating ULSI/VLSI circuit designs"