TOOL CORPORATION http://www.tool.co.jp

# Versatile Layout Platform -

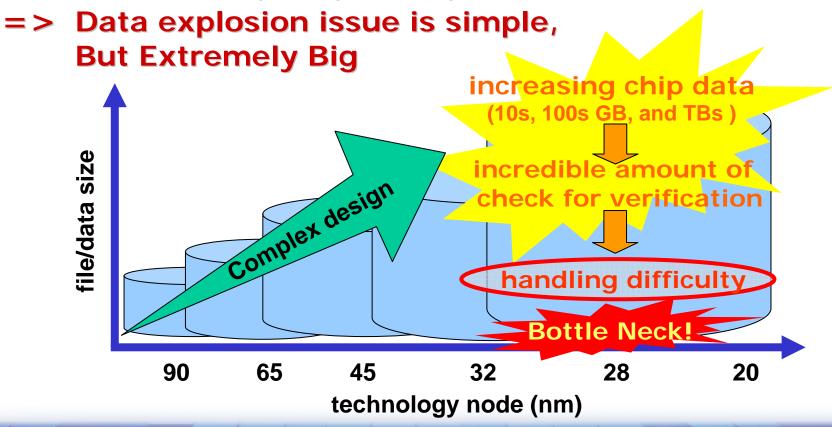

## Various Issues in Advanced Process

#### ■New issues

- Power, Signal Integrity, DFM, DFT, so on

- Many verifications and checks are required

- All those data is getting too large to handle

**TOOL CONFIDENTIAL**

- How to handle incredible amount of data?

- How to check sea of results of verification?

- How to satisfy needs in each process?

(usually an individual tool in each process)

- ✓ For Physical Design

- ✓ For Failure Analysis

- ✓ For MDP (Mask Data preparation)

- Not only <u>performance</u> but also <u>useful functions</u> to improve the quality & the productivity

LAVIS Layout Analyzer Can Provide Solutions

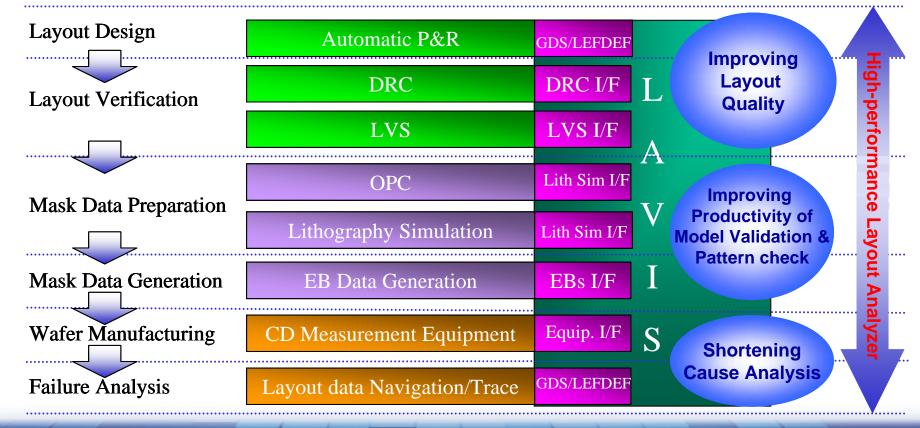

## High-performance Layout Visualization Analysis Platform

- LAVIS provides:

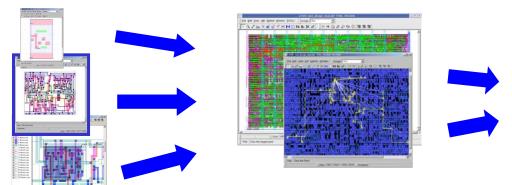

- Common operating super high-speed and huge data display

- Powerful analyzing capabilities and abundant Interfaces

- A simple, cost-effective, easy to use solution

# LAVIS High-performance Multi-use Layout Analyzer

- Super high-speed and enormous layout data display

- Stress free opening and drawing any large layout data

- Improve layout visualization checking productivity tremendously

- Powerful layout analysis capability to improve the quality of Layout Design and the productivity of MDP and Silicon FA

- Multi-format and many sophisticated check/debug functions and utilities for Layout Verification, Si Failure Analysis, and Mask Data Preparation

- Abundant interfaces for physical verification, litho-simulation, CD-measurement, and Failure Analysis

- Various interfaces with popular DRC/LVC, DFM/OPC tools and semiconductor equipment like Inspection and Failure Analysis

- Enable to reduce Verification/Analysis Cost & TAT by using affordable and convenient Layout Analyzer

- Fill the gaps between the automatic and the nonautomatic checking processes in the one-pass sign-off design & verification flow

- Common layout platform across the entire physical design flow

# Versatile Layout Platform

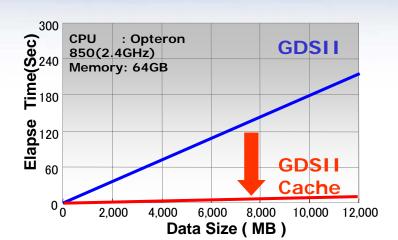

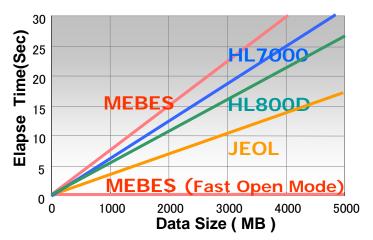

### Super High Performance

**■**Opening Time

GDSII 1GB / 20sec. x1/20(use cache)

EB 1GB / 10sec.

**■ Drawing Time** 2-3sec.

■Track Record

GDSII 500GB / 4 hours (memory size: 100GB)

Other viewer can handle such huge data with High-performance?

# Powerful Functions & Useful Interfaces

#### ■ Visual debug & check capabilities for all needs

#### **Functions:**

- **Node-Trace**

- Overlay & Image Paste

- Boolean Operation

- LEF/DEF, Find net&cell

- **GDS/OASIS Simple Edit**

- Synchronized Views

- Data Cutting out

- Set & Save Markers

- Measurement & Search

- Compressed data

- direct read

- Color Map Display

- X-section & 3D Display

- Remote Viewing

#### Interfaces:

- Calibre DRC Interface

- DRC & LVS I/Fs

- Litho. Sim. I/Fs

- CD Measurement I/Fs

- Other Equipment I/Fs

#### **Utilities:**

- Virtuoso env. conv.

- Boolean operation

- GDSII/ASCII conv.

- Cache file make

- Density calculation

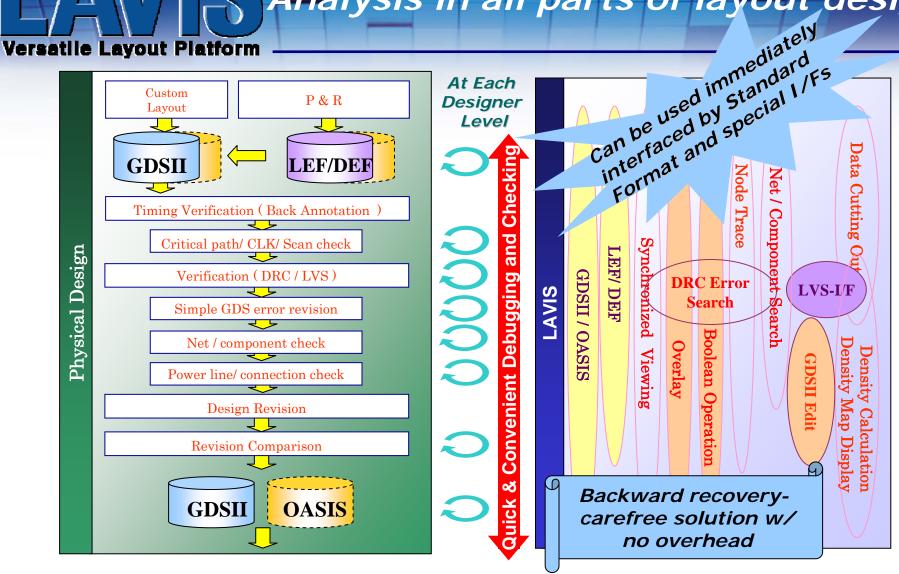

### Physical Design Flow

## Quick & Convenient Visualization Analysis in all parts of layout design

Improving the Efficiency of your Layout Design Work and the Layout Quality

#### In Physical Design Process

(even for Analog/Mixed-signal Design)

LAVIS enables to improve your <u>Layout Quality</u> and <u>Efficiency of Your Work</u> by yourself using with a sense that you can check **CONVENIENTLY**

- what you want

- when you want

- -all you want

in all parts of layout design with **No Iteration** and **No Overhead**

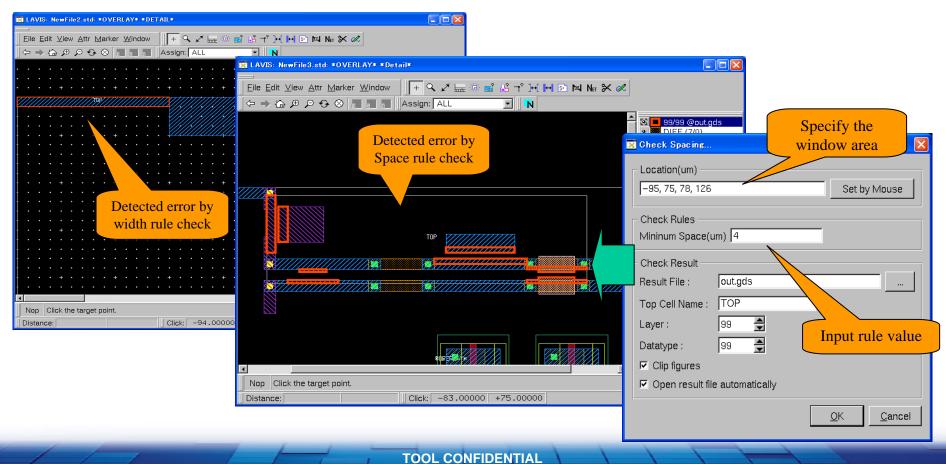

- Quick layout rule check in specified areas and on traced nodes - relatively small area As "simple layout checker"

- Width/Space/Area/Density/Sliver Check

- Length/Perimeter/Redundant Via/Resistance Calc.

- Cell/Component/Block/IP, and Pins (Ports)

- Connectivity of Power, CLK, Signals -> electrical short

- ECO check/compare difference/no-difference

- X-talk, Parallel lines, Symmetry properties, etc.

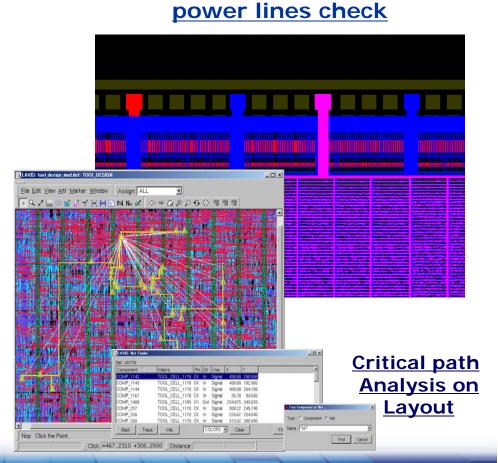

- Check and debug of DRC/LVS results at a chip level and large nodes as Power line As "layout debugger"

- Quick look at entire error distribution at chip level

- Check and what-if analysis of timing issues like critical path/CLK

- Check large node as PWR line for EM restriction

#### Incremental Checking to Improve the Quality

Enable to improve the Design Quality at individual designer level by Checking Incrementally at any design stage as Cell, Block/IP and a chip level whenever you want to avoid big issues at the last minute filling the gaps between automatic and nonautomatic checking flow

The total verification TAT is decided on by how to improve the quality at lower design levels Final sign-off verification as DRC/LVS

No big fatal impact!

**Cell level**

Block/IP level

**Chip level**

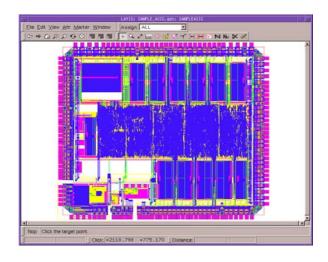

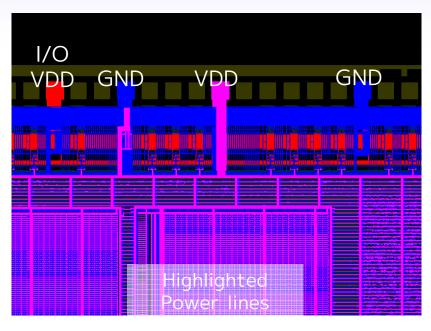

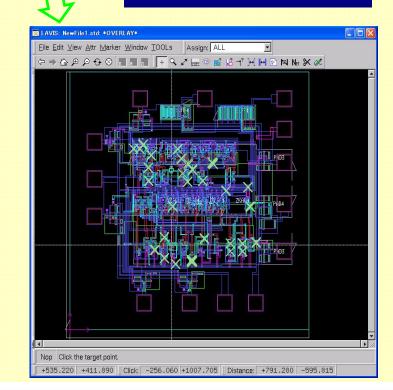

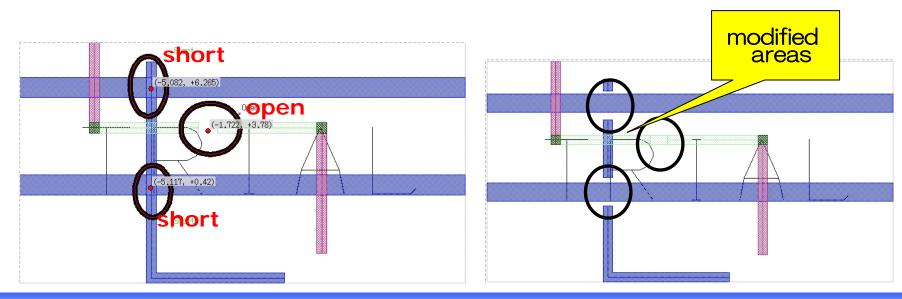

### Layout Check at chip level - Power/CLK/SCAN, DRC, TA -

Enable to check a layout at chip level with high performance for tracing huge nodes like Power, Clock, Scan clk, Busses, and error distribution, critical paths

Eile Edit View Attr Marker Window IOOLs Assign: ALL POR MINIMARK TO BE SEED OF SEE Nop Click the target point. Chip level +535.220 +411.890 Click -256.060 +1007.705 Distance: +791.280 -595.815

Quick look at error distribution

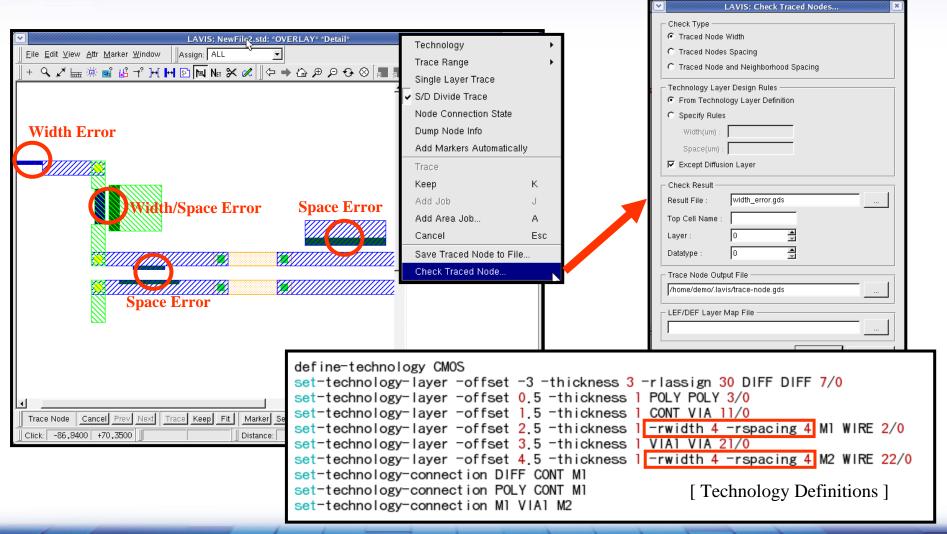

### Simple Rule Checking

## Area Specified Rule Check (1)

#### New Minimum Width/Space Check

> Minimum width/space check within the specified window area is available

### Area Specified Rule Check

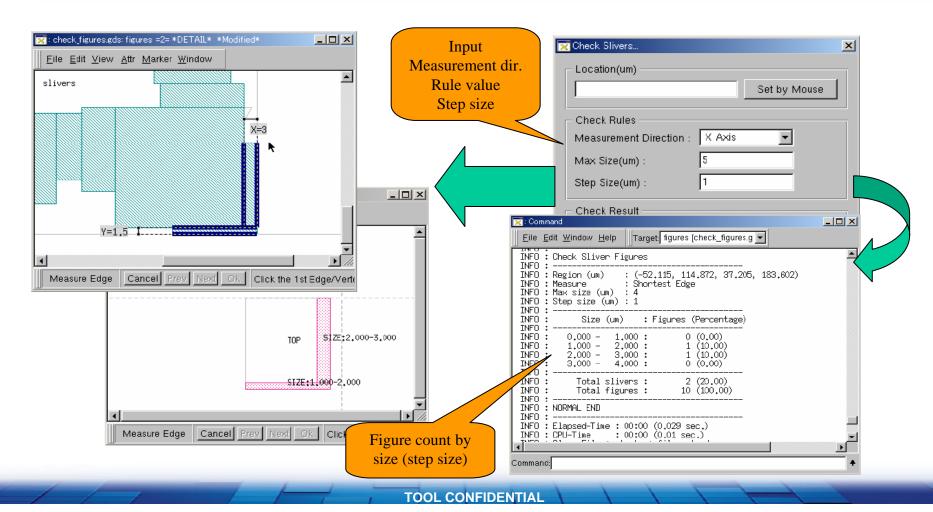

#### **New Sliver Check**

> Sliver check within the specified window area is available

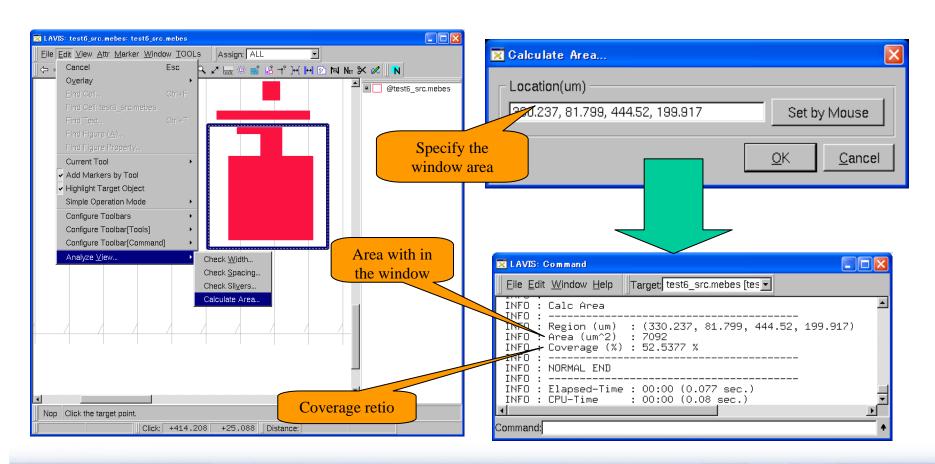

## Area Specified Rule Check (3)

#### New Area Calculation within the specified window

> Enable to calculate Area/Coverage within the specified window area

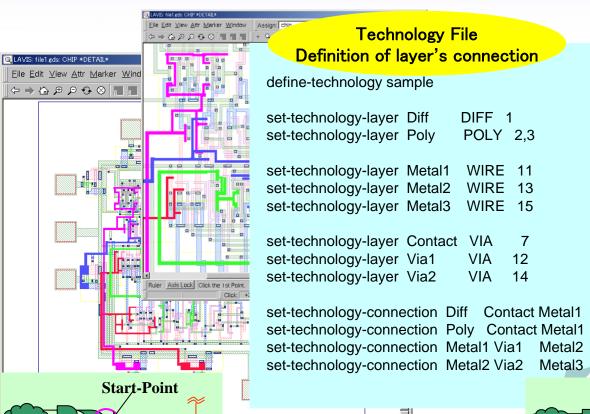

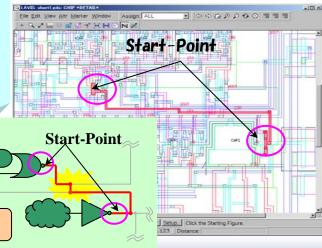

### Node Checking on GDS

#### Tracing Node and Short

#### **Easy to start node-trace analysis**

.235 Distance:

- Only GDS is needed

- Simple Tech. File

- Trace & Highlight of the same nodes

- Trace the shortest connection of 2 points

- Detect a location of electrical short.

**Short Trace**

## Intelligent Node-Trace (1) Versatile Layout Platform Intelligent Node-Trace (1) -- X-Talk checking --

■Simple rule check for nearby figures to the traced node

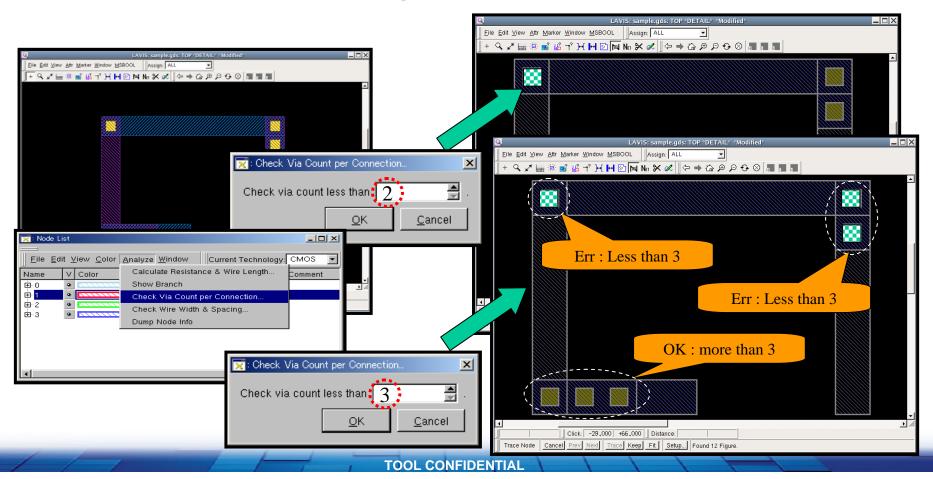

#### Node-Trace Additional Function (3)

=>Redundant Via rule check: Check Via Count per Connections

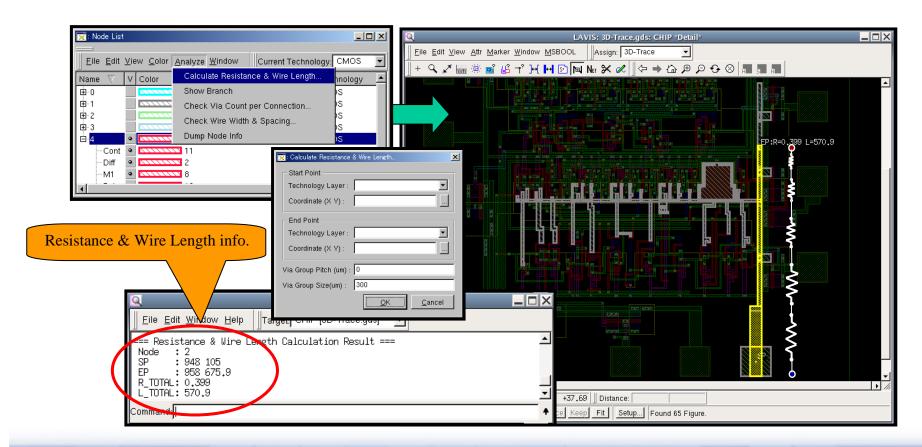

### Intelligent Node-Trace (3)

-- Resistance & Wire Length info --

#### **Node-Trace Additional Function**

=> Resistance and Wire Length can be calculated and displayed

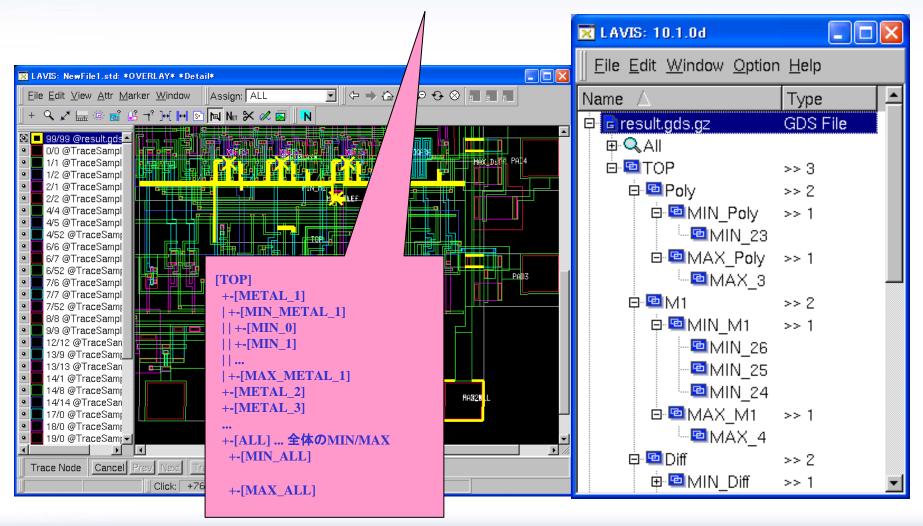

## MinMax Wire Width by each tech. layer

=> Display Min/Max by each technology layer

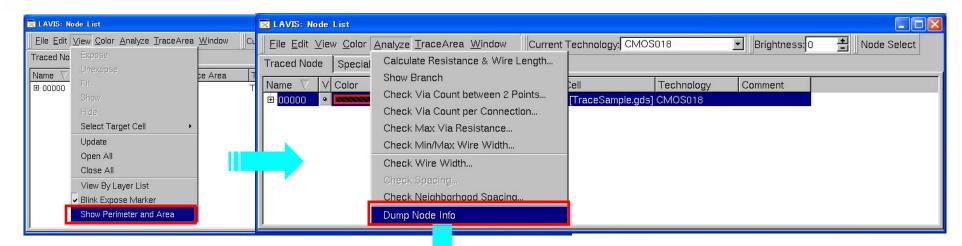

### Area and perimeter of Traced Node

=>Node List can display an area and a perimeter information of traced node

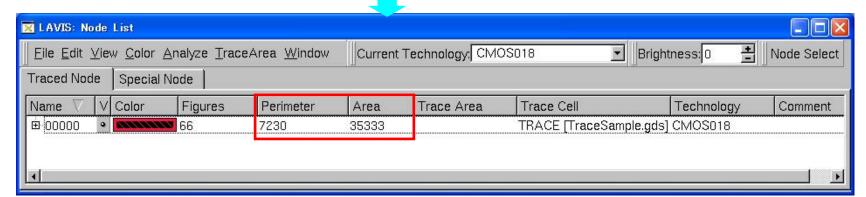

#### Check wire width between 2 points **Versatile Layout Platform**

**TOOL CONFIDENTIAL**

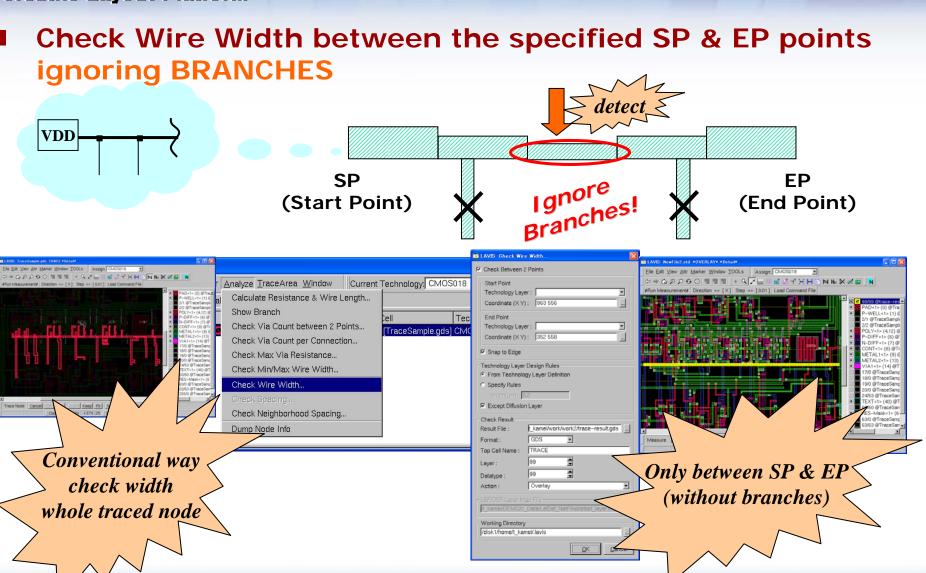

# High performance node tracing - Node Trace Data Base (NT-DB) Versatlle Layout Platform

Batch process Node-trace flow

♦ Batch process node-trace flow

All nodes extracted at chip level once are saved as a node DB

♦ Case of power lines tracing

Enables to check easily wires of huge net with many figures, and multi power lines running at chip level using a node DB

10s~100s times faster than interactive mode!

### Layout Comparing Check

### ECO Check & Compare

Nop Click the Point.

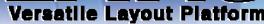

- **■**Overlay & Image Data Paste

- □Overlay Display GDS/LEFDEF/EBs

- □Quick Comparison & Difference Check

- ■Easy to set Scale/Origin/Rotation

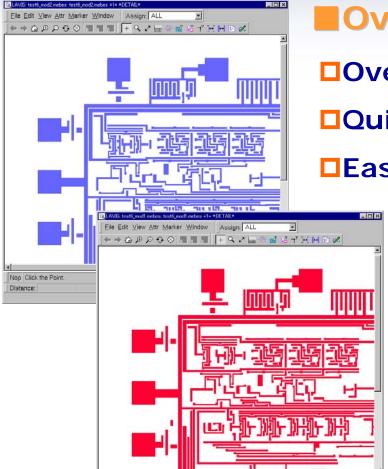

## Versatile Layout Platform - ECO Check & Compare (2)

#### **■**Boolean Operation & Display

- ■Boolean Operation of overlaid data

- XOR

- AND

- OR

- SUB

- ■Display the result in GDSII

- **■**List up the results

- ■Enable to navigate all geometries by selecting the line in the checklist

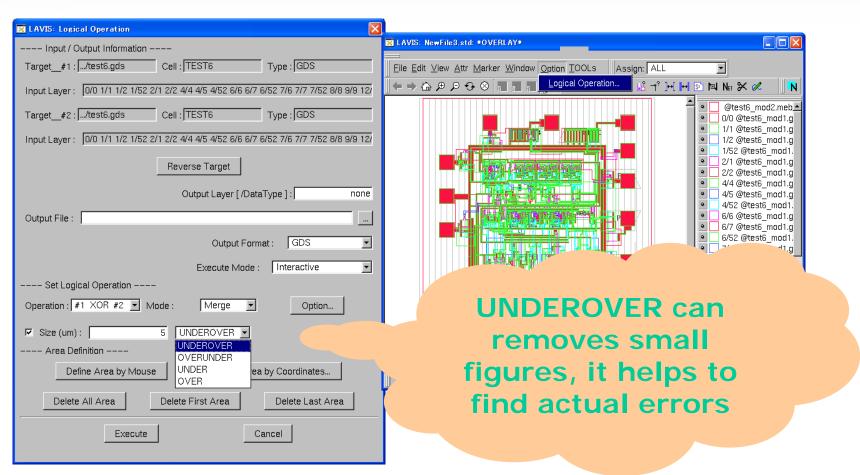

## Logical Operation / Ivlogic has Versatile Layout Platform Logical Operation / Ivlogic has Resize Function

=>LogicalOperation/Ivlogic, resize(underover, etc) operation after boolean operation.

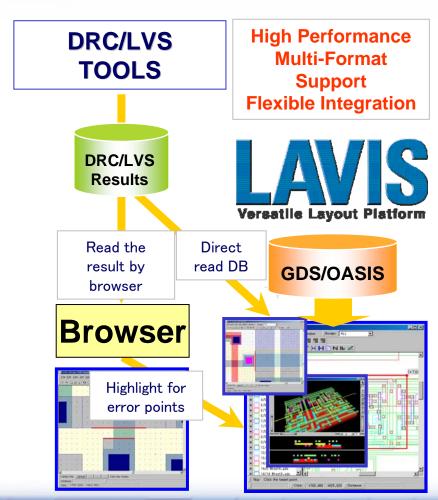

# I/F with Sign-off DRC/LVS Tools

#### Layout Verification Error Analysis and Layout Revision **Vers Layout Verification** Error DB lverrdb2qds one-by-one review & revision **Check List** File Item Window 👉 H 🔿 Setup Viewing Option ... B-R1.5 (# 4) (Nwell enclosure of Ndiff < 0.5um / (Substrate/Well contact Active to Nwell edge) B R2.1 (# 3) (NDIFF width for interconnect < 6.0) B R2.6 (# 7) (NDIFF overhang of Poly < 4.0) B-R6.3 (# 3) (Poly spacing < 4.0um) © 003 (949.000, 595.354)–(952.000,606.646) © R6.4 (# 2) (Poly spacing to Pdiff or Ndiff < 3.0) ⊞ R8.2 (# 4) (Metal1 spacing < 3.0um) ⊞ R8.3 (# 4) (Metal1 enclosure of Contact < 1.0um) custom layout capable editor Nop Click the Point. +29.6320 +16.7360 Click +11.8440 +16.0740 Putmage +17.7880 +0.6620 Out of capacity Edit Simple

**LAVIS**

**Quick look at entire** error distribution

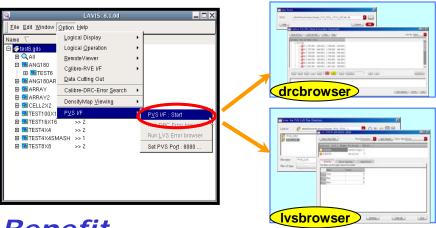

# Versatile Layout Platform

### Assist for DRC/LVS analysis

- I/F with 3<sup>rd</sup> party tools -

Interface with 3<sup>rd</sup> party tools

- Calibre-I/F of Mentor

- PVS-IF of Cadence

(ex) Cadence PVS-I/F

#### **Benefit**

- ⇒ Easy and Flexible interface using Remote Viewing Environment

- ⇒ Direct read for DRC Error ASCII DB output by CalibreDRC

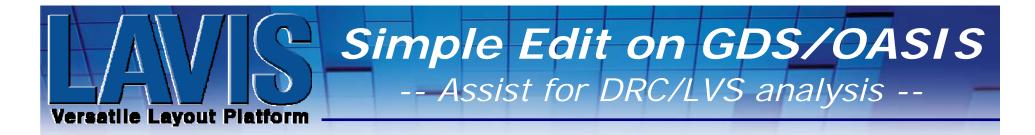

# ECO & Hot fixing On GDS/OASIS

#### Hot Fix for Layout Verification

- Quick layout modification add/delete/move text, elements & cell

- Create new GDS/OASIS data

For fixing a tiny bit of errors to get the short free data

⇒ Fix the DRC/LVS errors in the early phase of design flow, feedback to the original data, and shorten the total verification TAT

## GDS Simple Edit Functions

| Items                            | Functions                            |                                             |                                                      |                                             |                                      |

|----------------------------------|--------------------------------------|---------------------------------------------|------------------------------------------------------|---------------------------------------------|--------------------------------------|

| File Handling                    | Create File                          |                                             |                                                      |                                             |                                      |

| Cell Handling                    | Create Cell                          | Copy Cell                                   | Delete Cell                                          |                                             |                                      |

| Figure, Cell Input               | Input Boundary                       | Input PATH                                  | Input TEXT                                           | Input Cell<br>(SREF)                        | Input Array Cell<br>(AREF)           |

| Figure, Cell<br>Selection        | Select Figure &<br>Cell              | Select Side of<br>Figure                    | Select Vertex of<br>Figure                           | Select<br>Multi-Figure                      |                                      |

| Selected Figure,<br>Cell Editing | Move Selected<br>Figure & Cell       | Copy Selected<br>Figure & Cell              | Delete Selected<br>Figure & Cell                     | Change Parameter of<br>Selected<br>BOUNDARY | Change Parameter of<br>Selected PATH |

|                                  | Change Parameter of<br>Selected TEXT | Change Parameter of<br>Selected Cell (SREF) | Change Parameter of<br>Selected Array Cell<br>(SREF) | Rotate Selected<br>Figure & Cell            | Mirror Selected<br>Figure & Cell     |

|                                  | Add Sequential<br>Figure             | Divide Figure                               | Move Selected<br>Figure & Side                       | Move Vertex of<br>Selected Figure           | Resize Figure                        |

|                                  | Figure Logical<br>Operation          | Selected Figure & Cell Instantiation        | Selected Array Cell<br>Expansion                     | Selected Cell<br>Expansion                  | Selected TEXT<br>Expansion           |

| Others                           | UNDO, REDO                           | Incorrect Figure Prohibition Mode           | Resume Function for Abend                            | QUIT Editing Cell<br>Information            | QUIT All Editing<br>Information      |

Available Not available

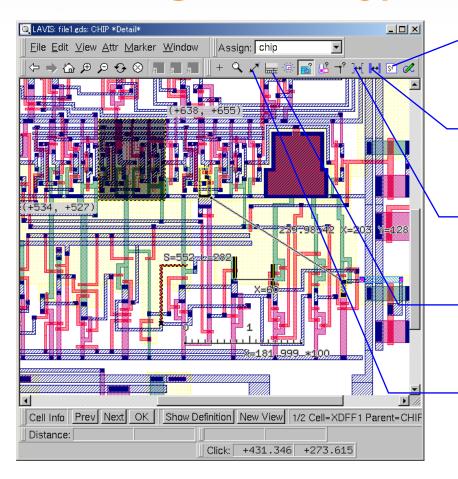

#### LEF/DEF Interface

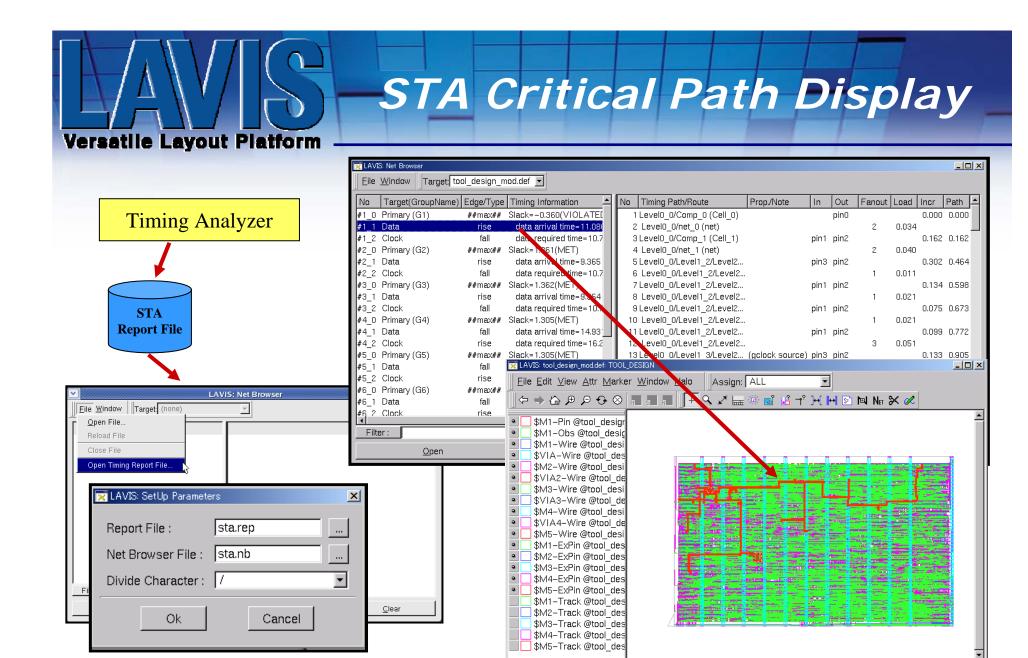

### Pursuing wire connection and Critical/CLK Path

**■** Trace net & component on LEF/DEF display

- Trace/Find Net & Component

- Visual Track/ Check of CLK Tree

- Visual Track/Check of Critical Path by TA

- Scan Path check, etc.

- Overlay LEF vs GDSII

- ■Check Cell/IP ports & Obstacles

LAVIS can read a timing report of TA tool

Nop Click the target point.

Distance:

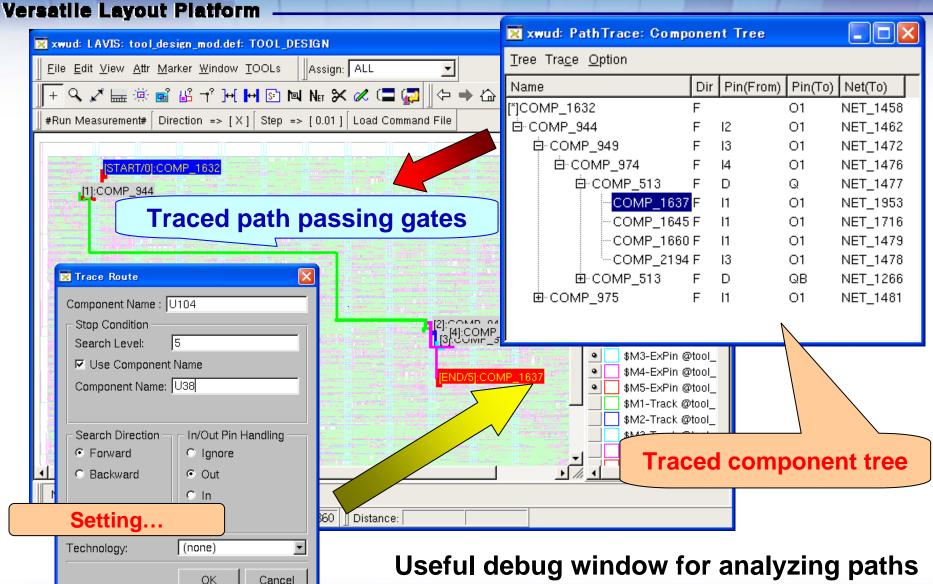

#### Gate-pass Route Trace - LEFDEF I/F

**Useful debug window for analyzing paths**

**TOOL CONFIDENTIAL**

#### Other Features

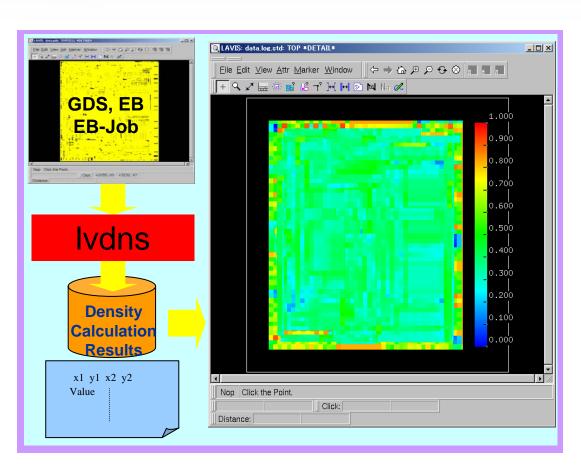

# Density Calculation Wersetile Layout Platform Wersetile Layout Platform Density Calculation & Map Display!

Displaying a color map for an analytical calculation result

- Geometry-based (Layout patterns) density calculation result

- Voltage drop calculation

- The density calculation utility is bundled in LAVIS

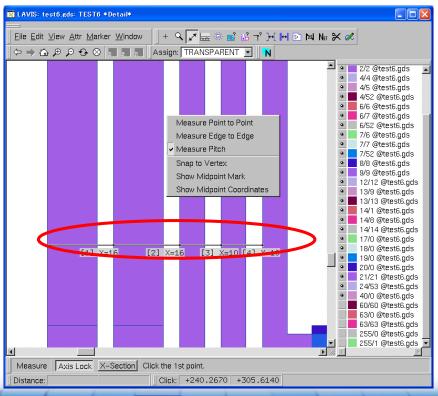

#### Measurement

■ Providing various types of measurement tools

Measure Area Tool

Area/Perimeter

Measure Figure Tool 2-figure interval

Measure Edge Tool 2-sided space/width

Ruler Tool (Scale)

2-point distance

Measure Tool

2-point distance

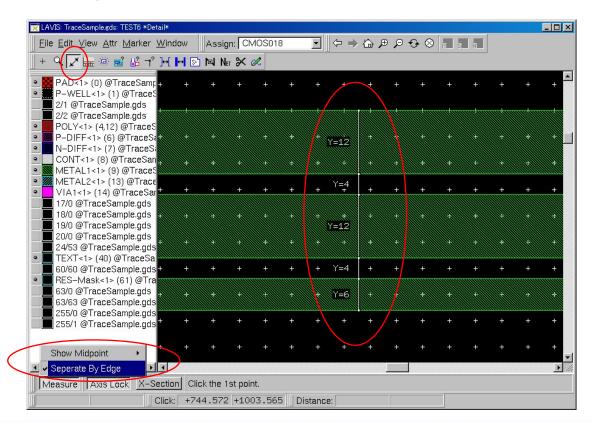

#### Measurement Tool has the new option

=> Line & Space can be measured at a time

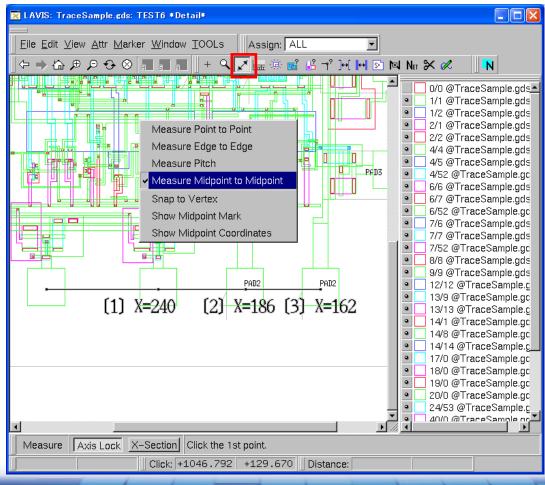

## Pitch measurement for L/S Versatile Layout Platform

#### 03. Pitch measurement for line & space

=> MeasureTool has pitch measurement function for L/S (detect the same side edge) Also it says the number which stands for how many pitch(es) from the end

=> "Measure Midpoint to Midpoint" can be available on MeasureTool

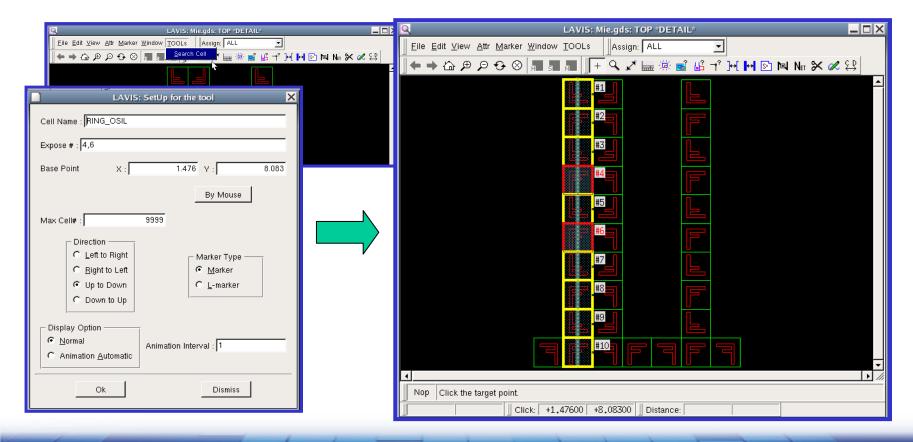

### Searching Cells

#### <>Feature: SerchCell

Easy finding cell for the specified view area and showing order number automatically

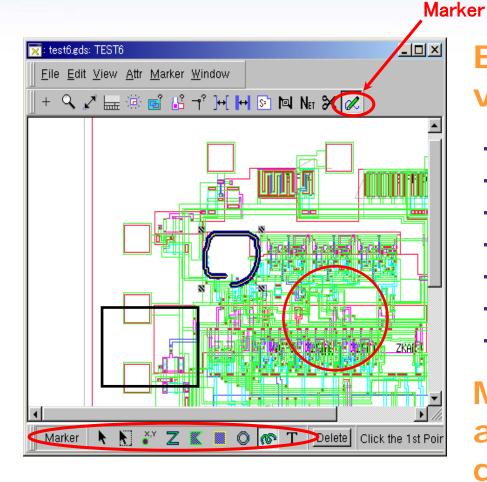

#### Markers

**Enable to set & save various types of Marker**

- Line

- Rectangle

- Polygon

- Circle

- Freehand

- Text

- Bitmap, etc ...

More Easy to do check and revision of layout data

By taking advantage of

LAVIS High-performance Multi-use Layout Analyzer

- Super high-speed & huge data display

- Powerful layout check and debug capabilities

- Abundant interfaces with popular EDA tools

for the physical design and verification flow

**LAVIS** can shorten Turn Around Time & provide the High Cost-Performance

http://www.tool.co.jp

E-mail: lavis@tool.co.jp