# Agenda

- Company Overview

- Dialite Products

- Competitive Analysis

- Customers

- Distribution Channels

# Temento Company History

| History                   | Temento History  1995 Company founded  1996 Test Services  1997 1 patent granted  2001 DiaTem Product Release  2003 DiaLite Product Release  Sales Channel Formation |                         |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| 0000                      | 1995                                                                                                                                                                 | Company founded         |

| MAGOO                     | 1996                                                                                                                                                                 | Test Services           |

| ionos<br>ofution          | 1997                                                                                                                                                                 | 1 patent granted        |

| ion<br>ion<br>ion<br>so   | 2001                                                                                                                                                                 | DiaTem Product Release  |

| Provide<br>SD 111<br>Sebu | 2003                                                                                                                                                                 | DiaLite Product Release |

| Ve<br>T                   | 2004                                                                                                                                                                 | Sales Channel Formation |

| Vati                      | 2005                                                                                                                                                                 | Sales Ramp-up           |

| NOTE THE                  | 2006                                                                                                                                                                 | 2 more patents granted  |

| 三                         | 2007                                                                                                                                                                 | DiaLite Power Edge      |

| e e                       | 2008                                                                                                                                                                 | DiaTem 3 release        |

|                           | 2009                                                                                                                                                                 | DiaLite 4.7 release     |

|                           |                                                                                                                                                                      |                         |

- Focus on the debug and verification of complex FPGA, SoC, and PCB designs

- 100 consumers and communications electronics customers worldwide

- Headquartered in Grenoble France, with sixteen, predominantly R&D, employees

- Unique core technology, three patents

- Two successful, mature product lines

The test and debug of complex PCBs

The verification and debug of FPGAs and SoCs post fabrication

Temento Confidential

PATENTED TECHNOLOGY

01011000100010101

# Diatem Overview

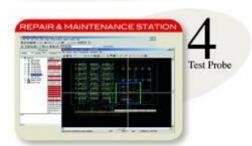

Diatem Lab is composed of 4 stations to test electronics boards throughout the product life cycle

A WorkStation running DiaTem

A Hardware JTAG Controller

Your Units Under Test

START TEST

START TEST

**Industrialization Station**

# 0111110001000101010

### AFTER DFT TECHNOLOGY ADOPTION

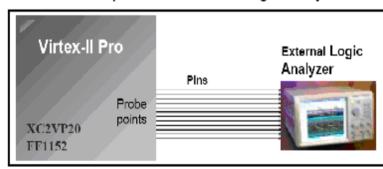

# Traditional Logic Analysis Method

Dedicated pins connected to logic analyzer

- Requires extensive dedicated I/O for debug

Driving signals to external I/O introduces additional problems

- Inflexible solution

- Difficult or impossible to add additional debug pins if needed

- Limited visibility to on-chip activity

# In System Debug Solution

# Integrate a logic analyzer in the FPGA GIVES:

- Access to the complete data bus

- Access to all internal design nodes.

- Operates at the full system speed

- synchronous the the design clock

• FPGAS ARE GETTING BIGGER, FASTER, EMBED LARGE BUSSES, DSP CORES, LOGIC ETC.. MAKES SIGNALS EXTRACTION INFEASIBLE!!

### **BOTTLENECK**

• PACKAGES ARE GETTING SMALLER WITH MORE PINS, DO NOT HAVE EXPOSED LEADS THAT CAN BE PHYSICALLY PROBED!

### **BOTTLENECK**

BOARDS ARE GETTING SMALLER WITH MORE LAYERS. TRACES ARE OFTEN BURIED INSIDE MULTI-LAYER PRINTED CIRCUIT BOARDS

TRADITIONAL METHODS RUN OUT OF STEAM

NO TECHNIQUES ON THE MARKET AVAILABLE TO COVER ALL CORNER CASES YOU

MISSED IN SIMULATION/EMULATIONON-CHIP VERIFICATION & DEBUGGING TOOL

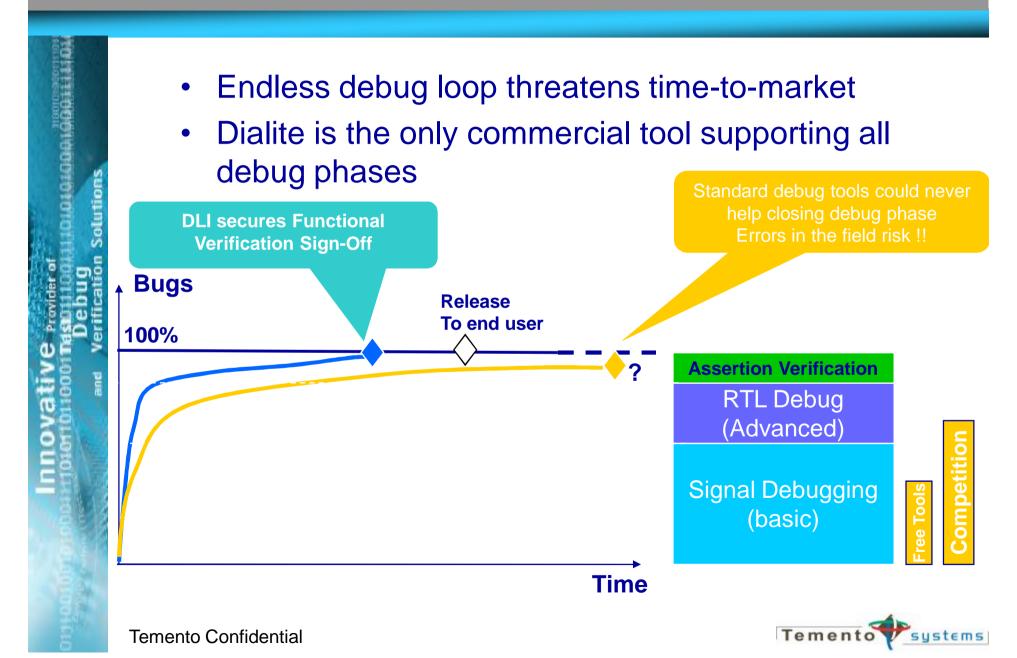

# Dialite Key Benefit

# DiaLite Opportunity Throughout Platform Flow

### **Prototyping / Emulation**

### **Market**

3K projects

### **Issues**

- External verification reduces performance of overall methodology

- Testing and debugging design internals hard to execute

### Design Progression

### **FPGA-based Designs**

### **Market**

20K design starts

### Issues

- Controllability and observability of internal signals restrictive

- Lack of effective verification methods e.g. no synthesizable assertions

### **SoC Designs**

### **Market**

3.7K design starts

### Issues

- Design to integration flow disconnected, making debug torturous

- System verification methods non-existent, complicating software hardware validation

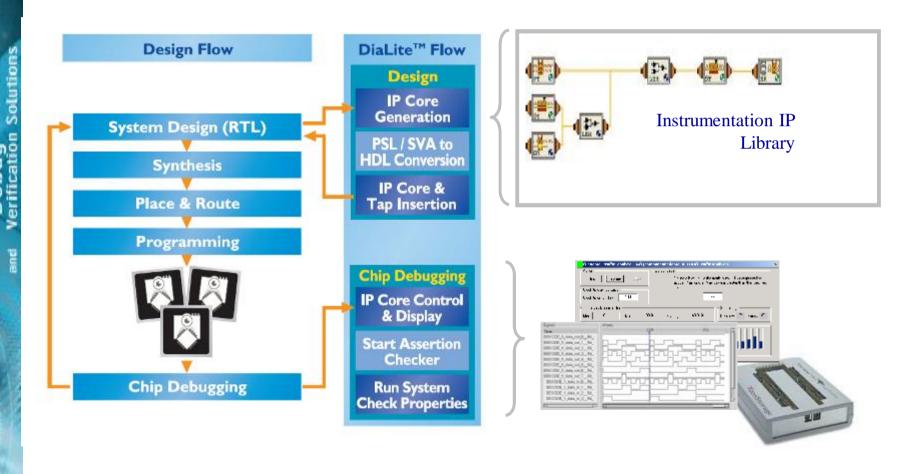

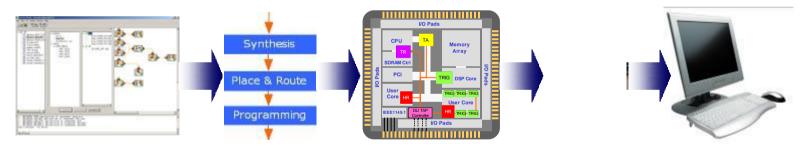

# DiaLite Design Flow

IP instrumentation cores are inserted at the RTL level.

101111000100010101010

# User Friendly Interface

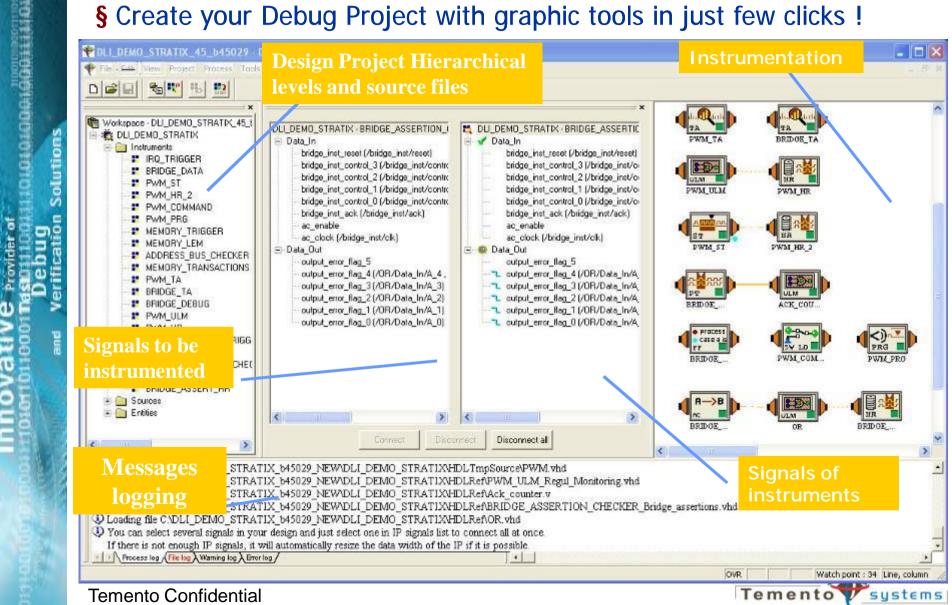

§ Create your Debug Project with graphic tools in just few clicks!

# Dialite Instruments Portfolio

Recorders

Verification Code Debug

## A Collection of 14 Debug IPS

101111100010001010101

**Parallel**

Switch & Leds

**History Register**

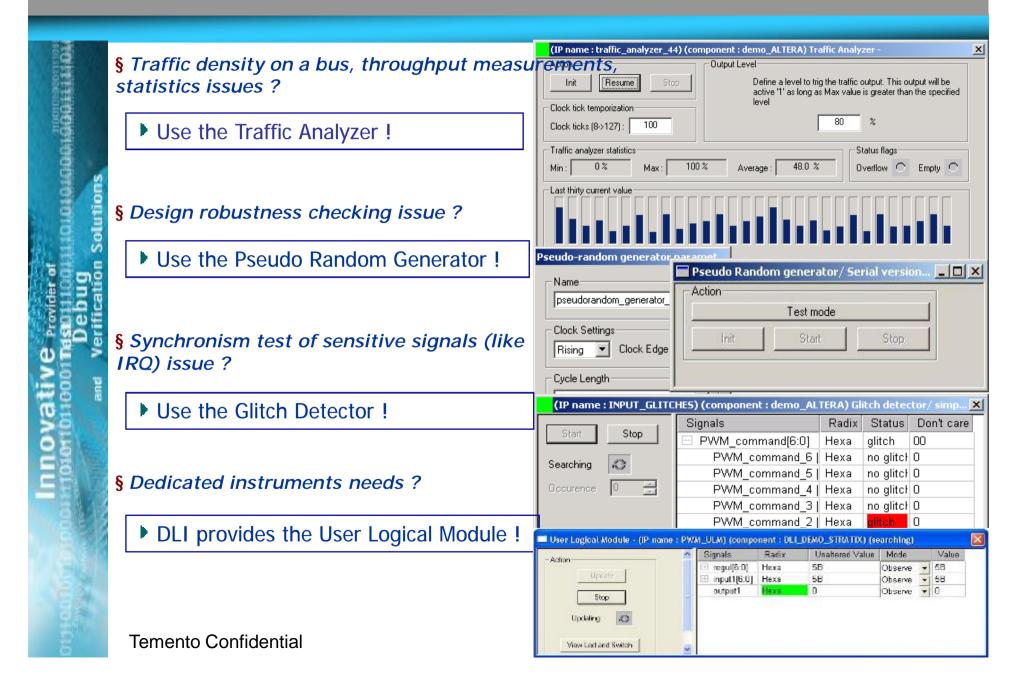

**Glitch Detector**

Pseudo **Random** Generator

**Transaction Register**

Logic Equation Module

**Traffic Analyzer**

Bus Range Checker

**AHB Bus Tracer**

**HDL Fault Finder**

**Assertion** Checker

User Logical **Module**

# An Instrument for each Issue

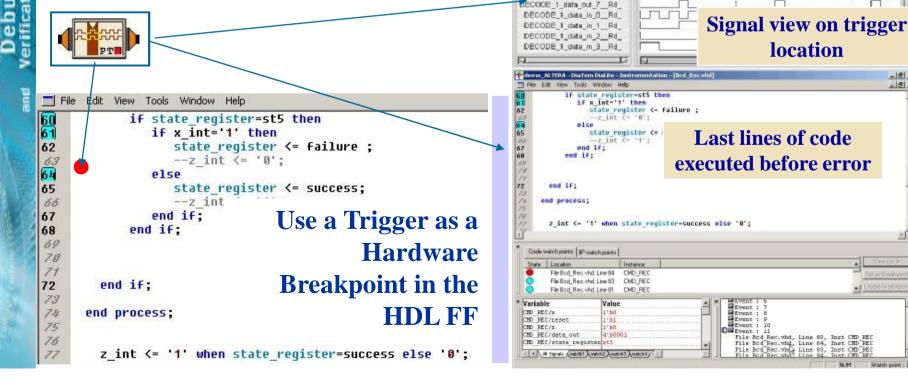

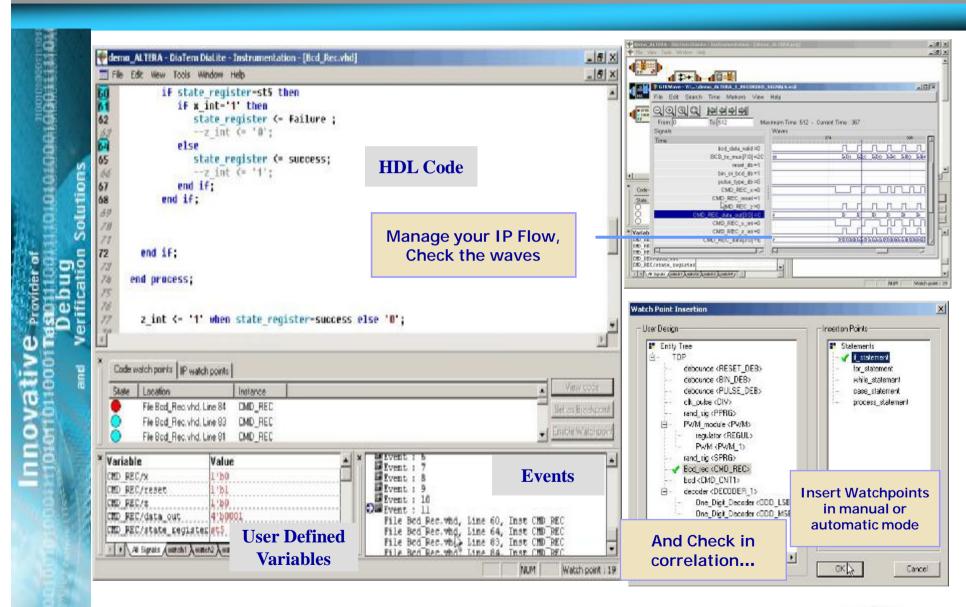

# DiaLite Power Edge & the HDL FF

DECODE 1 data out 0 Rd DECODE 1 data out 1 Rd

DECODE 1 data out 2 Rd DECODE 1 data out 3 Rd DECODE 1 data out 4 Rd

DECODE 1 data out 5 Rd DECIDEE 1 data out 6 Rd Waves

location

§ HDL Fault Finder expands debug productivity by providing a bridge between signals on silicon and RTL code!

▶ When a trigger condition happens, it becomes easy to find error into

**HDL** code

0101000100010101

▶ Using HDL FF, you're directly pointed to the error:

# DiaLite Power Edge & the HDL FF

routoon permiter of the state o

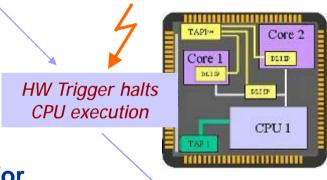

- § Hard/Soft Co-Debug is easily performed using DiaLite dedicated TAP option :

- ▶ Leave the native TAP to Soft Debug tools

- ▶ Use dedicated TAP (Altera, Xilinx) for DiaLite Instrumentation

- § Link your C code to an HDL Debugger

- § Increase performance of instrumentation monitoring

- § Leave instruments in the production chip for acceptance or maintenance

Temento Confidential

# DiaLite Platform & the AC

Definition: An Assertion is the execution of a Property, which itself can be seen as a fragment of an executable specification

- § The Assertion Checker (AC) IP imports the assertions & embeds them into your chip

- § DiaLite Platform is the ONLY one to use your formal properties written during System Specification and to:

- § Run them On Silicon

- § Run them At Speed

- § Get Real-Time feedback & coverage

next ((acknowledge && grant) until\_valid). mrc always (sigl; sig2) -> (sig3; sig4[\*2] before (sig5 == 0)) **Properties** Design Specification Formulation User Design Ps Generation Design Instrumentation User Verification Design Units Synthesis, Place & Route Chip programming On-Chip Debugging On Chip ABV

Temento Confidential

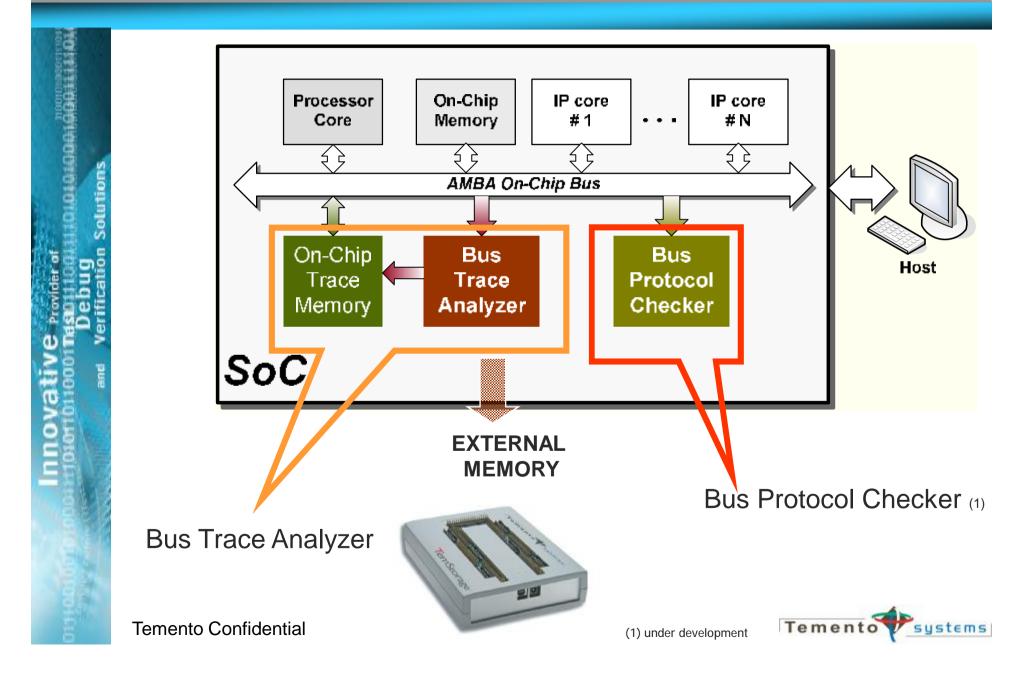

# Instrumentation for bus analysis and debug

# INTEGRATED TRACE AND ANALYSIS SOLUTIONS FOR EMBEDDED PROCESSORS

Processor Processor IP core IP core Core 1 Core N #1 # V Wrapper Wrapper Wrapper Wrapper AMBA System Bus Platform Signal Monitor & Tracing Wrapper Wrapper Signal/Timing Abstraction Bus Trace ₹OK Memory Tracer Master Traced Event Transition data Trigger **JTAG** ata States interface Trace Compression Data Packing SoC Bus Tracer Traced data output form Trace Port

- JTAG Interface

- user can setup the tracer through JTAG port

- Signal Monitor & Tracing (Signal/Timing Abstraction)

- to determine when and which signals should be monitored

- Trace Compression

- to compress the trace size generated from timing/signals abstraction module

- Data Packing

- packs the trace data generated from the data compression module and buffer the output data

- Trace Output

- transfers the trace data to host (PC)

- Stored in/out on-chip memory

Temento Confidential

10111100010001010101

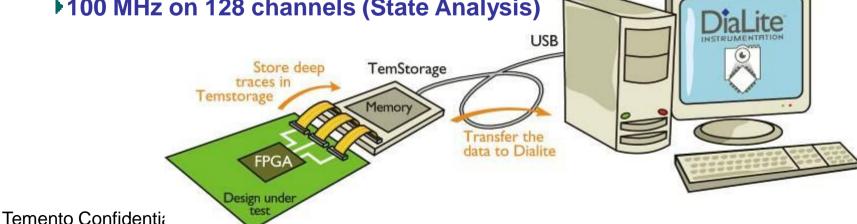

- § TemStorage frees the FPGA resources of your Debug project!

- Store large amount of Data outside your DUT and stream them to the Host PC through USB

- Seen in DLI as a Memory device for Test IPs working with RAM or Registers (like History or **Transaction Registers)**

- TemStorage parameters can be customized from **DiaLite GUI**

- ▶ 1GB Memory / 220 data channels /

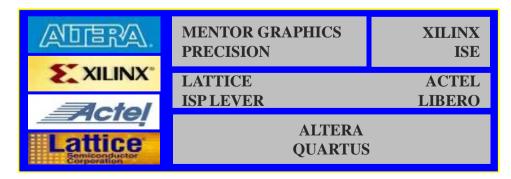

# Device Independence

- § Same Debug Possibilities whatever is your FPGA Manufacturer

- § Same Debug Possibilities whatever is your Design Flow Provider

- § Start a project with a manufacturer, move to any other!

- § Split it between several FPGA targets, DiaLite is Multi-FPGA compatible!

- § DiaLite can run mixed VHDL / Verilog Designs

- § Assertions can be written in PSL or SVA

- § Possibility to use a dedicated or the native TAP of the FPGA manufacturer

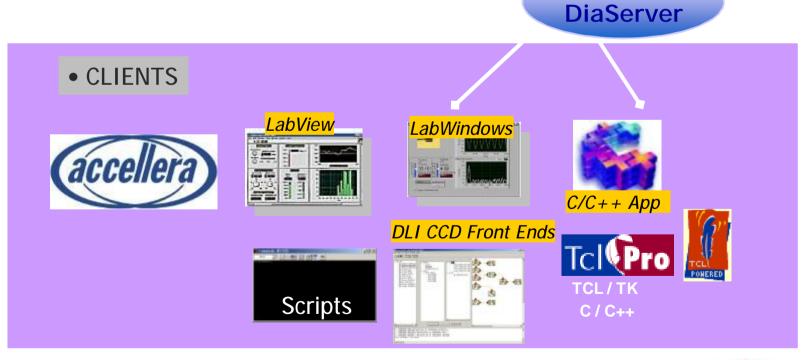

§ DiaLite is based on popular Standards Verilog, VHDL, PSL, SVA, TCL, C++

§ Easy integration into any EDA environment using script and extended API

§ DCOM based client-server architecture (DiaServer), enable rapid third party integration

Temento Confidential

- Powerful platform verification through hardware methodology

- Complete solution of advanced techniques now available in hardware

- High performance verification fully leveraging hardware

- No software verification environment running with emulator or prototype

- Easy to use, consistent throughout flow, debug & verification process

- Works throughout existing flow, easy to use instrumentation and analysis

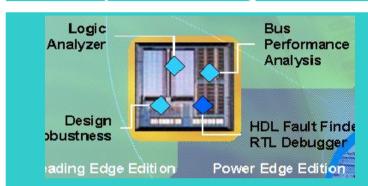

| Package             | Application                               |  |

|---------------------|-------------------------------------------|--|

| DiaLite LeadingEdge | FPGA Design                               |  |

| DiaLite PowerEdge   | FPGA Design & SoC Prototyping             |  |

| DiaLite Platform    | FPGA Design, SoC Prototyping & SoC Design |  |

| Hardware Storage    | All                                       |  |

### DiaLite makes a powerful addition to multiple methodologies

### **FPGA Verification**

Enable platform verification throughout design flow

# DiaLite INSTRUMENTATION

### **HDL Debug Extension**

Extend HDL debug into systems, hardware integration, FPGA

### **SoC Verification**

Transform hardware software, design to integration, verification

Temento Confidential

# Emulation / Rapid Prototyping Acceleration

Inline verification increases performance and functionality

| ON CHIP INSTRUMENTATION (FPGA) - COMPETITIVE MATRIX |                                                                                                                                         |                            |                  |       |           |                     |           |           |            |                  |  |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------|-------|-----------|---------------------|-----------|-----------|------------|------------------|--|

| Competitive Matrix                                  |                                                                                                                                         | Temento                    | Novas            | Aldec | Mentor    | Lattice             | Altera    | Xilinx    | Synplicity | Actel            |  |

| Validation &<br>Verification                        | Assertion Checking<br>o Hardware Assertion<br>Instrumentation and<br>Validation                                                         | DiaLite<br>Platform        |                  |       |           |                     |           |           |            |                  |  |

| Debug &<br>Verification                             | Bus Analysis<br>o ARM AHB Protocol<br>o ARM AXI Protocol <sup>1</sup><br>o OCP Protocol <sup>1</sup><br>o IBM Core Connect <sup>1</sup> | All DiaLite                | Debussy<br>Verdi |       | Spiratech |                     |           |           |            |                  |  |

|                                                     | RTL Debugger<br>o C-Debugger Interface<br>o State Machine Debugger                                                                      | DiaLite<br>Power Edge      |                  |       |           |                     |           | Identify  | Identify   | Identify<br>(AE) |  |

| Design<br>Instrumentation                           | Instrumentation<br>o Multi- Vendor FPGA<br>Support<br>o Multi Vendor Synthesis<br>Support                                               | DiaLite<br>Leading<br>Edge |                  |       |           | ISP Tracy<br>Reveal | SignalTap | ChipScope | Identify   | Identify<br>(AE) |  |

|                                                     |                                                                                                                                         | Precision                  |                  | YST   |           |                     |           |           |            |                  |  |

XST

**Precision**

Synplify

Note 1 - Temento Development Roadmap

XST

QUS

Synplify

Multi-Vendor Support Proprietary Partial Solution

Precision

Precision

**Synplify**

QIS

XST

**Synplify**

**Synplify**

Design

**Synthesis**

# Customer Base

- 40 DiaLite Stations running

- Broad range of electronic segments covered

- Strong presence in Japan and Europe

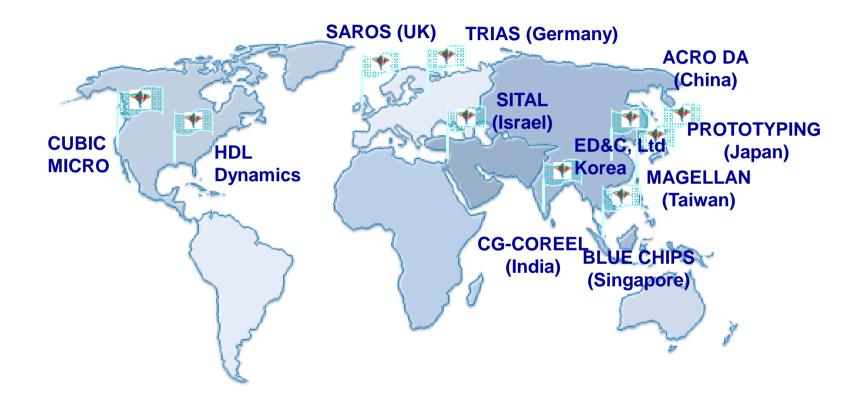

# **Distribution Channels**